Enclosed you will find a first version of the lab manual that goes with the LD12 Computer Kit. It is intended as a supplement to a standard text on digital logic such as:

Dietmeyer -- Logic Design of Digital Systems -- Allyn & Bacon

Clare -- Designing Logic Systems Using State Machines -- McGraw-Hill

It can also be profitably used in a course in computer architecture. Texts useful here are:

Hill & Peterson -- Digital Systems: Hardware Organization and Design -- Wiley

Peatman -- The Design of Digital Systems -- McGraw-Hill

Foster -- Computer Architecture -- Van Nostrand

It has been copyrighted in its present form and duplication should be limited to educational institutions using the LD12 Computer Kit. I am actively engaged in extending the book to cover more advanced design techniques at which time I hope to publish it.

David E. Winkel

## (1) INFORMATION REPRESENTATION

How do we talk to computers? Unfortunately not as easily as we talk to other people. Think of the ways humans can communicate--writing, speaking, hand signs, facial expressions, etc. One of the rude awakenings that new students get when introduced to the subject is how stupid computers are! Human thought must be transcribed onto punched cards or some other machine readable media, and even the most trivial errors (misplaced commas for example) will completely confuse the computer.

But even punched cards hide the inner level of communication within a computer. Internally a computer understands voltages only. That in fact is why we input information on cards. Once a card is punched it is relatively easy to send it through an electromechanical device which will convert the information punched on the card into voltages which can be interpreted by the computer.

Thus, information must be transformed into forms that electronic circuits can understand. To make this perfectly clear let us consider a light switch which in many ways is similar to some of the elementary building blocks used to make a computer. Of course the switch understands only one thing--physical movement--is it on or off? Imagine two people, a room, and a light switch.

Turn on

the light.

O.K., I

understand.

I don't.

Do you see the problem? The verbal command has not been transformed into a form the switch understands.

Turn on

the light.

O.K., I'll flip

the switch.

Now I'll respond.

Now something happens! This may seem trivial but it brings the problem into the open.

What sorts of things do computers (and logic circuits) understand? We repeat--VOLTAGES!

How many different voltages? TWO!

Why only two? Because engineers have been unable to build reliable circuits for anything but two.

What are these voltages?

H = high = approximately 3.0 volts

L = low = approximately 0.2 volts

That only two voltages are recognized by digital logic is fundamental to the whole field. It is so important that a name has been given to it--BINARY--which means that only two stable states exist. Examples of binary devices are:

Switches - either ON or OFF

Punched Cards - any given position either has a hole punched out or it doesn't

Logic Circuits - put out either a high or a low voltage

Magnetic Tape - a given spot has either a north pole or south pole pointing up

These two different states are commonly given names of 1 and 0.\* For example if the choices in the left-hand column are arbitrarily made, the meanings of a 1 and 0 are shown in the right two columns.

| If a 1 is chosen to mean              | then a 1 means    | and a 0 means        |

|---------------------------------------|-------------------|----------------------|

| switch is open                        | switch open       | switch closed        |

| a given spot on a card is punched out | hole at that spot | no hole at that spot |

| High                                  | High              | Low                  |

| a given spot is a north pole          | north pole        | south pole           |

| L                                     | L                 | H                    |

Again let us emphasize. You, the designer, can choose the meaning of a 1. Of course, you must have some way of telling the world what your

\*As the designer you can choose what a 1 means.

choice was so your design can be understood. As we will see a standard notation has been devised to make your choice evident.

Also, understand that 1 and 0 are simply names for the two states of a binary device. 1 and 0 do not have a numerical meaning. You could use X and Y for the two names and everything would work as well. Of course it would be unconventional.

Now we come to an important topic. Can ordinary human (decimal) numbers be represented by only H and L voltages? If not then it will not be possible to build a computer. The answer must be yes.

Let us consider the process of counting, using ordinary decimal digits. Of course there are 10 different digits 0, 1, 2, 3, 4, 5, 6, 7, 8, 9. Suppose we are counting rocks falling out of a chute

\* = ROCKS

DECIMAL NUMBER

REPRESENTING THE ROCKS

|       |   |

|-------|---|

| *     | 0 |

| **    | 1 |

| ***   | 2 |

| ****  | 3 |

| ***** | 4 |

| ***** | 5 |

| ***** | 6 |

| ***** | 7 |

| ***** | 8 |

| ***** | 9 |

What do I do now? I have run out of digits. We solve this by a very clever trick called the carry.

We get a carry of 1 out of the units column into the tens column and change the 9 to a 0.

\*\*\*\*\*

10

This process always works. Suppose we have 99 rocks and 1 more falls out of the chute.

$$\begin{array}{r}

9 \quad 9 \\

\underline{+ \quad 1} \quad \text{change 9 to a 0} \\

1 \quad \text{carry 1 into the next column} \\

+ \underline{9} \quad \text{change the 9 to a 0} \\

\hline

1 \quad 0 \quad 0 \quad \text{carry 1 into the next column}

\end{array}$$

We have defined a general process for counting using the digits 0 - 9.

The same process will work if we have only two digits 0, 1. Now a 1 will be the largest digit you can have in any column just as a 9 was the

largest digit you could have in a given column in an ordinary number. We call numbers represented in such a manner BINARY numbers. Perhaps a better phrase would be BINARY representation since what we will be doing is representing the number of rocks by 1's and 0's. The same could be said about the decimal representation for the same pile of rocks which uses 0's through 9's.

\* = ROCKS

### BINARY REPRESENTATION

\*

0

1

What do we do now? We have run out of binary digits!

- a) Change the 1 to a 0

- b) Put a carry in the next column.

\*\*

\*\*\*

10

11

What do we do now? Well, this is exactly like the case of 99 rocks in decimal. Both 9's were changed to 0's and a 1 carry was put into the next column to make 100. In binary, 11 would change to 100 since in binary 11 is the largest two-digit binary number you can have just as 99 is the largest two-digit decimal number you can have.

\*\*\*\*

\*\*\*\*\*

\*\*\*\*\*

\*\*\*\*\*

\*\*\*\*\*

\*\*\*\*\*

\*\*\*\*\*

etc.

100

101

110

111

1000

1001

1010

We see that it really is possible to represent numbers using just two symbols, 1 and 0. There is a problem in that a binary 11 is indistinguishable from a decimal 11. But a binary 11 really equals a decimal 3. We need some way to tell what kind of representation we are talking about. For this purpose we use a small subscript:

binary  $11 = 11_2$

decimal  $11 = 11_{10}$

A more mathematical way of looking at either binary or decimal numbers is the place value system. In this system a digit's value depends on the column it is in. For example, in decimal we have a 1's column, 10's column, 100's column, etc. Take the decimal number 432 and label the columns starting from the right with column 0.

| column number | 2 | 1 | 0 |

|---------------|---|---|---|

| 4             | 3 | 2 |   |

| column number | description  |

|---------------|--------------|

| 0             | 1's column   |

| 1             | 10's column  |

| 2             | 100's column |

| etc.          |              |

In fact  $432_{10}$  really means  $(4 \times 100) + (3 \times 10) + (2 \times 1)$ .

A similar thing can be done in binary except now

| column number | description |

|---------------|-------------|

| 0             | 1's column  |

| 1             | 2's column  |

| 2             | 4's column  |

| 3             | 8's column  |

| etc.          |             |

Now  $101_2$  really means  $(1 \times 4) + (0 \times 2) + (1 \times 1) = 5_{10}$ .

Thus we see that a 1 represents the presence of a power of 2 and a 0 its absence.

How the 1's and 0's in a binary number are in turn represented inside the computer by voltages is again the designers choice. Some designers represent a 1 by H, others do the opposite. The symbols used by the designer will make his choice clear.

Now for another piece of jargon. The individual 1's and 0's in a binary number are called BITS (B I nary digITS).

The only way to feel comfortable with binary numbers is to count to  $64_{10}$  in binary. The student is urged to do this now. So you can check yourself along the way.

$$\begin{aligned}

13_{10} &= 1101_2 \\

19_{10} &= 10011_2 \\

33_{10} &= 100001_2 \\

63_{10} &= 111111_2

\end{aligned}$$

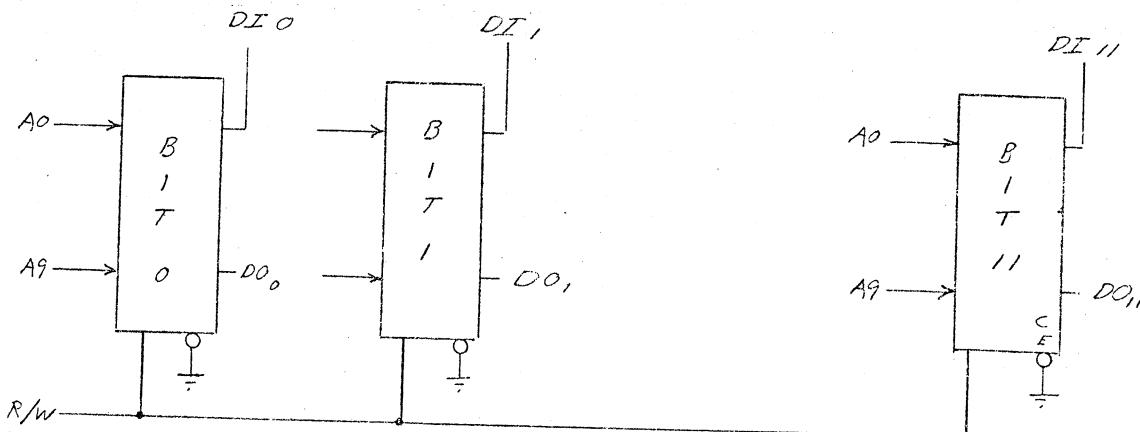

Let's take a break and discuss a less weighty but related subject--numerical accuracy. As you know from hand held electronic calculators, the more digits the more accuracy you can get. The same is true for binary computers. The smallest have eight bits of accuracy and some of the very large, fast scientific machines have 60 bits. The design in this book is a 12 bit machine.

Another bit of jargon--for our machine 12 bits of data is called a WORD. Thus this machine has 12 bit words whereas the Control Data 6000 series of computers has 60 bit words. The IBM 360-370 series has 32 bit

words. There are more PDP-8 minicomputers in the field than any other single type of computer (>25,000 installed), the PDP-8 has 12 bit words. Most new minicomputers being produced have 16 bit words since it is a nice compromise between cost and accuracy.

There is another parameter besides bits/words that is important in describing memories. That is the number of distinct words of data that can be stored. A fairly typical minicomputer would have four thousand (4k) words of storage. Large scientific machines may have millions of words of storage. Fortunately from a learning standpoint a small memory is as good as a large one and far cheaper.

Now let's get back to binary numbers. These numbers are elegant since they can represent any decimal number with only two symbols, 0 and 1. Remember this is necessary for internal use in a computer. They also have several disadvantages. One of them is it takes more binary digits than decimal digits to represent a given number. For example take 110010<sub>2</sub>. That is equal to 50<sub>10</sub>. It is far easier for a human to keep track of the two digits in 50<sub>10</sub> than the six in 110010<sub>2</sub>. A simple shorthand has been developed for binary numbers to collapse the number of digits a human has to work with. The trick is to start at the right side of the word and group the bits three at a time.

|     |     |

|-----|-----|

| 110 | 010 |

| 6   | 2   |

Now take each 3 bit group and convert it to a single number between 0 and 7. Now you have to remember only the binary numbers between 0 and 7. The resulting number is called an octal number. Why? (Hint: Decimal numbers have 10 distinct digits, 0-9; binary numbers have 2 distinct digits, 0, 1). To show a number is octal we write a small subscript 8 to the right of it. Converting between octal and binary is now simple. The process is best shown by examples:

binary ----> octal

|        |    |

|--------|----|

| 1011   | 13 |

| 11001  | 31 |

| 111010 | 72 |

octal ----> binary

|      |                 |

|------|-----------------|

| 6410 | 110 100 001 000 |

| 37   | 011 111         |

| 14   | 001 100         |

All of the commands for the computer will be given in octal because it is such a convenient shorthand.

## (2) COMBINATIONAL LOGIC (The Logic of Here and Now)

7

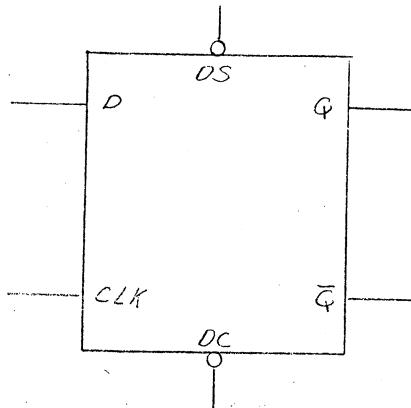

There are two main classes of digital logic circuits, combinational (sometimes called combinatorial) and sequential. We will need both types to accomplish our goal of building hardware that will execute a flow chart.

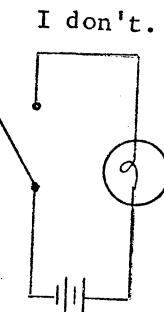

Combinational circuits act on information represented by H and L voltages and immediately produce an output. Actual circuits take a few nano seconds, which is close enough to immediate (light will travel 1 foot in one nanosecond). This class of circuits is the simplest to understand so we will treat it first.

In general we will not refer to 0's and 1's to represent our data since we are more interested in the voltage which represents it. The reason for this is simple. When you check a circuit the only thing you will be able to test are voltages. As we will see a set of symbols has been devised that gives you these voltages directly at a given point in a digital circuit. It is then a simple matter to place a logic probe at that point and get a visual display of the information. The logic probe used in the lab has small green and red lamps for display. When a given point is L the green lamp will turn on. The red lamp will light for a H input.

Let us now go over the symbols which describe digital logic.

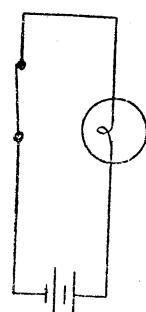

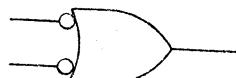

INVERTER

AND

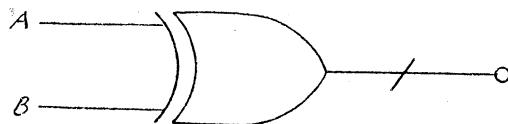

OR

special purpose element

Do not worry at the moment about the function of each of these symbols. Each will be introduced in due course. Let us discuss some of the general properties of the symbols.

- 1) The shape uniquely identifies its logic function except for the rectangle where this information is supplied by the device name.

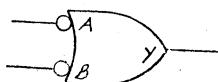

- 2) Inputs and outputs (copper wires) are represented by lines going into and out of the symbol. For example:

- 3) Outputs are always on the right; inputs are always on the left, top, or bottom. Thus, we know that in the above example the wires on the left are inputs and the single wire on the right is an output and we can now label it as follows:

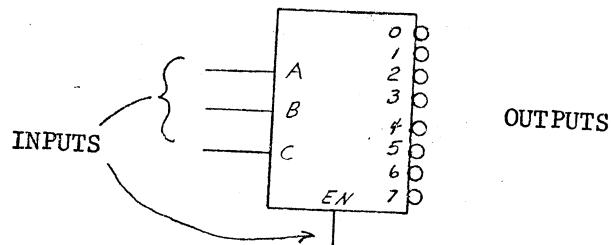

Another example would be a decoder. At this point of course you don't know what a decoder is. Nonetheless if I draw one

for you you should be able to tell which lines are inputs and which outputs.

4) The symbols are important since they quickly convey a large amount of information pictorially. The pictorial aspect should be emphasized. The eye can quickly encompass a large drawing with many symbols on it and get the overall picture. Just as easily the eye can zero in on a small portion of a large drawing and extract a great amount of detail. This can be difficult using words or even equations. Very soon you will be thinking of digital logic in pictorial terms since it is so easy and convenient.

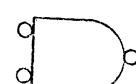

5) Voltage polarities are easily shown. The convention is that a small circle represents a low voltage and its absence a high voltage. For example suppose I have a special purpose circuit called a lamp driver. Its function will be to accept an input voltage and turn a lamp on or off on the basis of this input.

Such circuits are very useful in a computer since they can be used to visually monitor a signal.

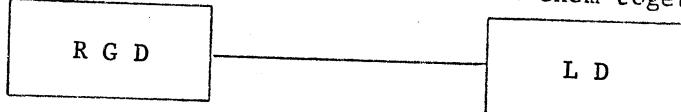

Let us now try to represent a lamp driver graphically:

a) It is a non-standard circuit. Therefore, its symbol will be a rectangle. Of course, a bare rectangle doesn't tell you much so we put a name inside it which describes its function.

b) Its output is on the right side of the box. Since its output is light and not a copper wire no output line has been drawn. An implied output (light) nonetheless exists.

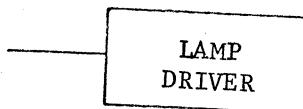

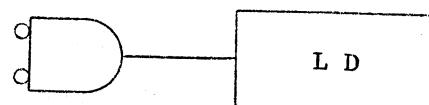

c) One vital piece of information is still missing. What kind of an input voltage turns on the light? In all of the lamp drivers used on your lab kit a high voltage turns on the lamp. Therefore, it would be drawn as below:

d) At this point review a) - c). You should be able to look at the above symbol and extract the following pieces of information just from the picture:

- 1.) it is a special purpose circuit (shape)

- 2.) presumably it turns a light ON or OFF (from its name)

- 3.) a high voltage will turn the light ON (its input line has no small circle on it)

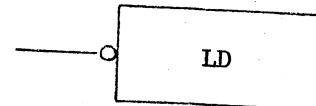

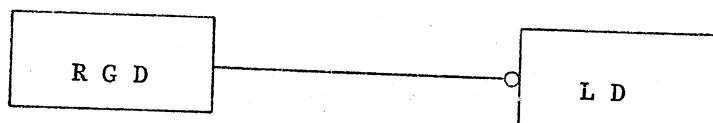

It is perfectly possible to design a lamp driver that will turn the lamp ON when the input voltage is low. In fact in your lab kit this could be done simply by unplugging the 7406 lamp driver IC (integrated circuit) and substituting a 7407 IC. How would this circuit be represented?

Small circle tells you that a low voltage is required to turn on the lamp

6) Note that the graphical symbol also suppresses much irrelevant information. It does not tell you what's inside the lamp driver. In fact we do not care. It could be transistors or perhaps a gremlin as long as the lamp was reliably turned on or off. The student should get used to looking at symbols as logical building blocks and forget about their internal workings. We are concerned only with the logical process of building a computer by interconnecting such building blocks.

One of the marvels of modern technology is the IC (integrated circuit). They are cheap, compact logical building blocks which have been carefully designed so that very diverse IC's can be interconnected without worrying about impedance matching, and all the other black arts of electrical engineering.

One last word of reassurance. Even professional computer designers are not concerned with the internal construction of an IC. If you are still not convinced take several years of high level electronics courses. But be warned--you won't be a better computer designer by virtue of your knowledge of the inner workings of IC's.

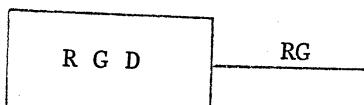

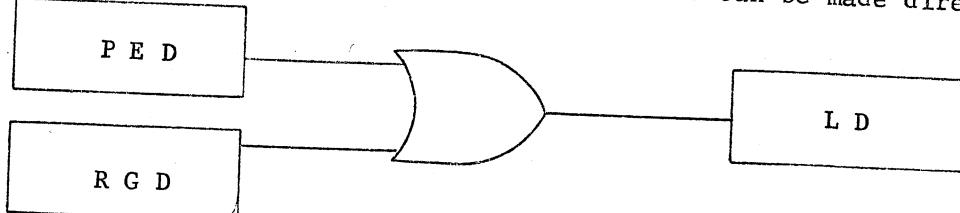

Let's define one more special purpose device and then experiment by connecting them together. The lamp driver required an input to activate it. We will design a special purpose circuit which produces an output which in turn can be input to the lamp driver.

Absence of a small circle indicates the output will be high when a red gorpisch is detected

From the above picture we can determine:

- 1) It is a special purpose circuit.

2) Its input is implied on the left. Since there is no input wire there must be some other means of inputting information to the device. (Perhaps there really is a gremlin sitting inside looking out a window on the left side. When he sees a red gorpsch he throws a switch which drives the output line high.)

3) The output will be H if a Red Gorpsch passes near the detector.

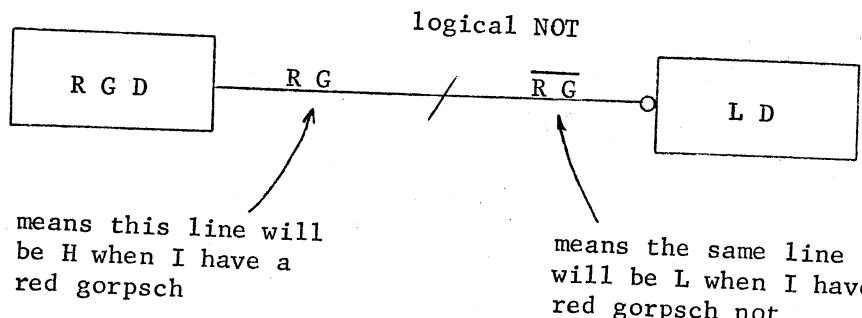

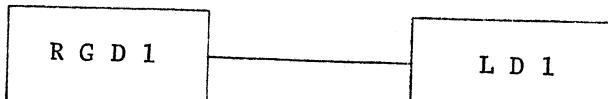

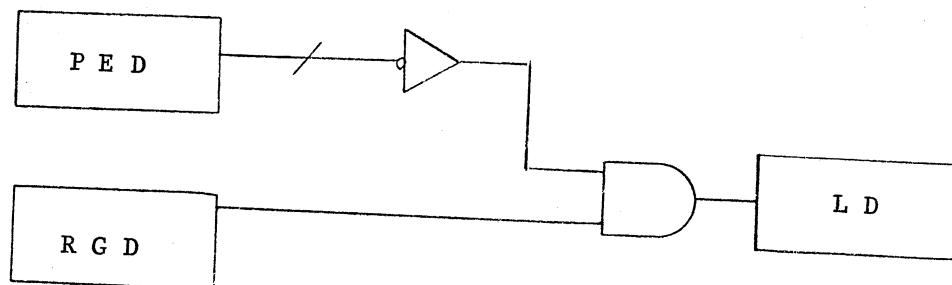

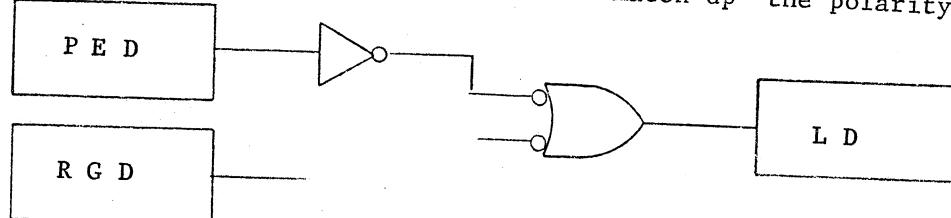

Let's take the two devices and hook them together.

When will the lamp light?

- a) Only when a red gorpsch passes near the detector. In that case the RGD output will go H and that is the polarity needed by the lamp driver to turn on the light.

- b) Note that only a red gorpsch will produce a H output--a green gorpsch would not, nor would a red elephant. Suppose a green gorpsch passed near the RGD. Its output would be L and the lamp driver would turn the lamp off.

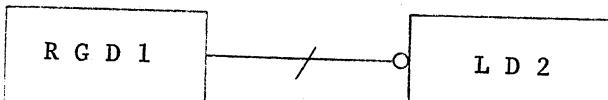

Now suppose we redesign the lamp driver so it will turn on the light when its input goes L. Again we hook the two devices together.

When will the lamp light? The light will be on only when the lamp driver's input is L. Since the RGD is a binary device it always outputs either a H or L. Its output will be L if there is NOT a red gorpsch.

We have just been introduced to the NOT operation of logic. This is a fundamental concept and we must explore it thoroughly.

First let us describe how we talk about the NOT operation. Suppose we have the red gorpsch detector by itself.

It would be logical to label its output line RG (standing for red gorpsch). A line labeled RG has no meaning by itself since we do not know whether an H or L represents a red gorpsch. To decide that we must trace it back to its source which will tell us its polarity. In this case RG = H.

There are only two voltages this line can have. The other one has to be L which corresponds to red gorpsch not. We write red gorpsch not as RG.

The crux of the matter is:

A LOGICAL NOT EXISTS WHENEVER A SIGNAL IS USED IN THE OPPOSITE POLARITY FROM ITS GENERATED POLARITY.

To remind ourselves that a logical not has happened we put a slash across the signal line.

Note: There is no special integrated circuit required to perform the logical not operation. It happens ANY time a signal is used in a polarity opposite from its generated polarity.

The logical not operation is important in digital logic for the same reason it is used in human thought. Many times it is easier to organize your thoughts if a certain condition is not true. An example would be: I will take a trip next week if my car does not break down. Most of us prefer to think that way rather than thinking of all the complications that could arise if it did break down. The concept is sharpened considerably in mathematics or programming where we may wish to alter our course of action on the basis of something being not true.

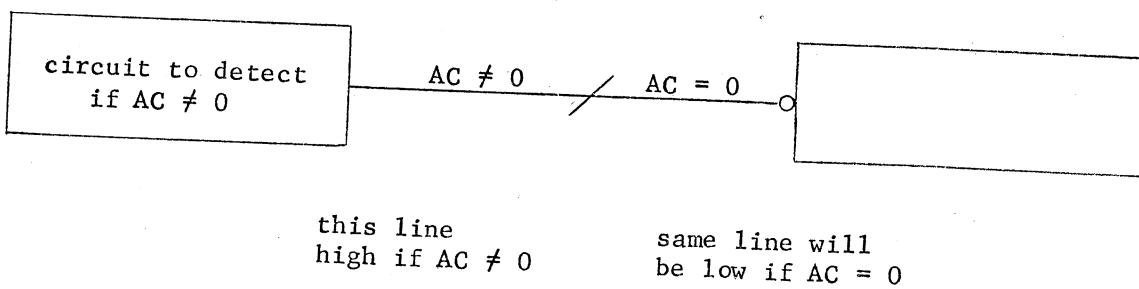

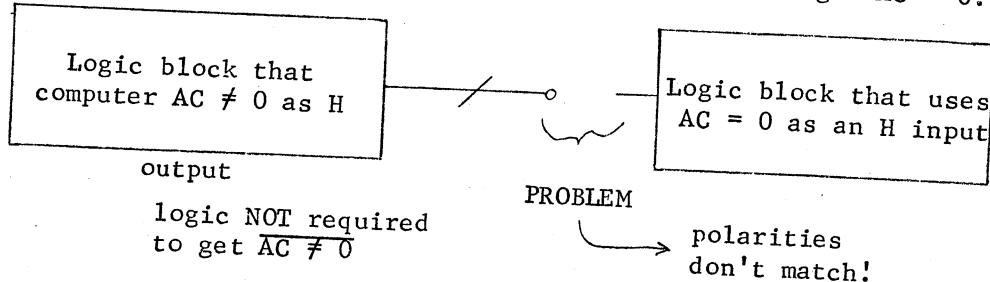

The same thought processes are used in digital logic. In the computer you will build, it is necessary to determine if the accumulator is equal to 0. (All 12 bits equal 0.) As you will see when you start to wire that section it seems more natural to compute  $AC \neq 0$ . It is certainly true

$AC = 0$

is the same as

$\overline{AC} \neq 0$

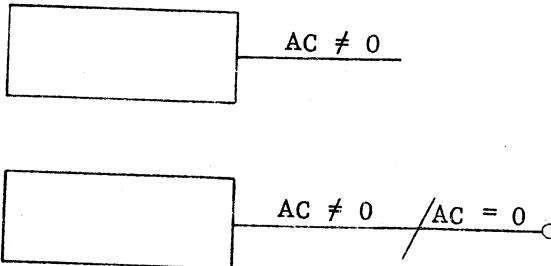

Suppose  $AC \neq 0$  was generated H.

If we want the not of  $AC \neq 0$  we must draw a slash across the line to remind ourselves that it must be used in a polarity opposite to its generated polarity.

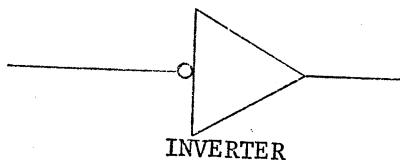

Now we come to another problem. We know that the circuit that is going to use  $AC \neq 0$  as an input will have to accept it as a L signal. Suppose it expects its inputs H? We need a device (called an inverter) that will fix up the polarity to be what we want. It has the property of outputting a signal of opposite polarity to its input.

Its symbol is:

This device will accept an L input and produce an H output. Of course it will also accept an H input and produce an L output.

Both behaviors are of course implied in the graphical symbol. As drawn, the behavior for low inputs is emphasized.

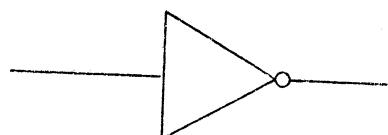

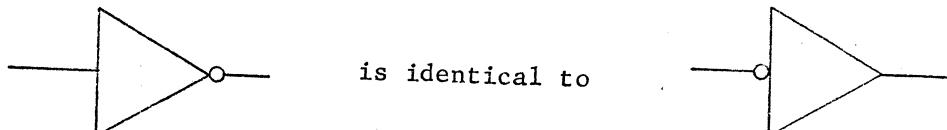

An entirely equivalent representation of the same device would be:

This symbol describes the behavior of an inverter for an H input, which produces an L output. Of course an L input will produce an H output.

Convince yourself that in fact:

Why draw it two different ways? The logic you are building will naturally dictate which representation to use. Let us reconsider the example of  $AC = 0$ . We go through the following steps:

- 1) We have a logic block which expects  $AC = 0$  to be input as an H signal.

- 2) With the IC's commonly available we find it more natural to compute  $AC \neq 0$  which is represented by an H signal.

- 3) We must do a logical NOT operation on  $AC \neq 0$  to get  $AC = 0$ .

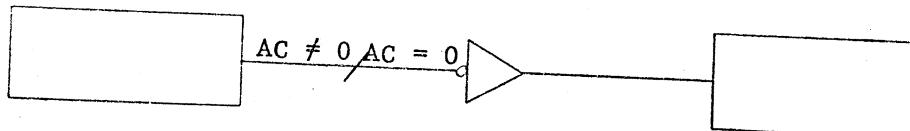

- 4) Solution: Place an inverter in the line to fix up the polarity.

- 5) In this case there is only one natural way to draw the inverter. Since the signal  $AC = 0$  is produced with an L polarity and we want to use it with an H polarity, we draw the inverter in a form which emphasizes its behavior with L inputs, namely:

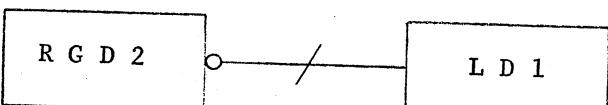

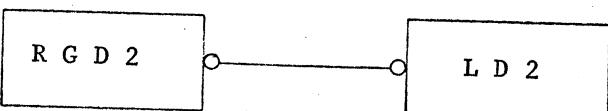

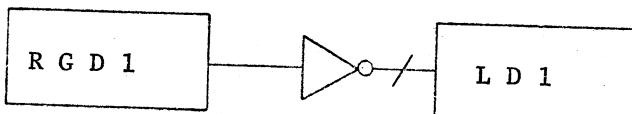

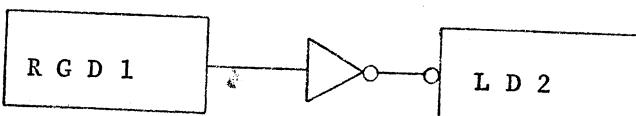

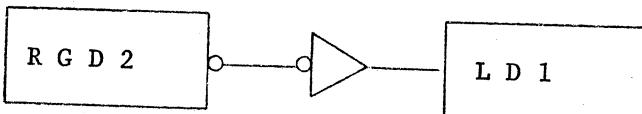

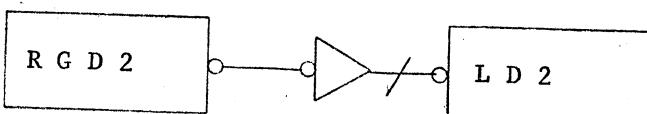

To review these concepts suppose we have two different red gorporpsch detectors RGD1 and RGD2 with the following properties:

Also assume two different types of lamp drivers, LD1 and LD2:

Let us hook up all four possible combinations and ask when the lamp will be ON.

red gorpssch

red gorpssch not

?

?

Do the same four cases but with an inverter inserted between the RGD and LD.

red gorpssch not

red gorpssch

?

?

English has several words used to express logical relationships. Without these words it would be difficult to speak. Try it without the following words: NOT, AND, OR, GREATER THAN, LESS THAN, EQUAL, etc.

Logic has similar constructs but a more limited vocabulary. In fact there are just three, NOT, AND, OR. We have covered the logical NOT operation in Chapter 2.

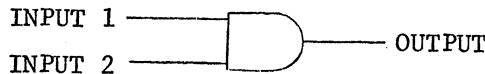

The definition of the logical AND is:

THE OUTPUT WILL BE TRUE IF ALL INPUTS ARE TRUE.

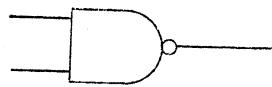

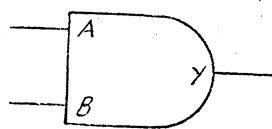

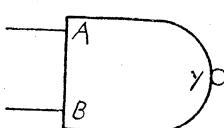

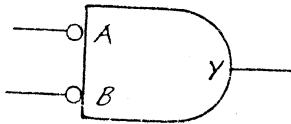

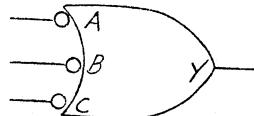

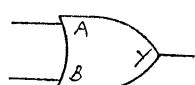

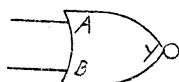

The definition of true follows the usual rules. Small circles represent L voltages. A non-circled line represents an H voltage. AND gates come in many flavors. The common AND gates and their IC catalog numbers are:

| NAME             | SYMBOL | CAT. # | BEHAVIOR                                     |

|------------------|--------|--------|----------------------------------------------|

| 2 input AND gate |        | 7408   | Y will be H if A AND B are both H            |

| 2 input AND gate |        | 7400   | Y will be L if A AND B are both H            |

| 2 input AND gate |        | 7402   | Y will be H if A AND B are both L            |

| 3 input AND gate |        | 7410   | Y will be L if A AND B AND C are all H       |

| 4 input AND GATE |        | 7420   | Y will be L if A AND B AND C AND D are all H |

| 8 input AND gate |        | 7430   | The output will be L if all inputs are H     |

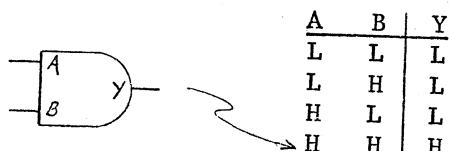

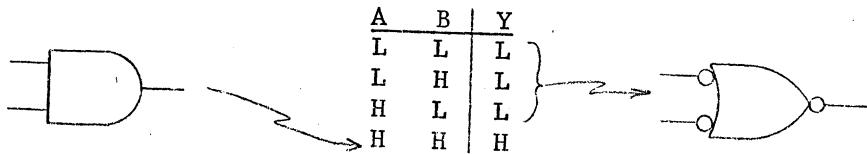

There is an equivalent way of describing the logical AND function. It is called the truth table for the device. All possible combinations of inputs are listed in a table and the output for each input combination is listed on the same line. Note that the truth table gives exactly the same

information about the 7408 as the graphical symbol. The symbol says that the output will be H only if A AND B are H. All other combinations will give an L output. The symbol has the useful property of emphasizing the last line of the truth table. As a designer if you need a logical AND in fact it is more natural to think only of the

last line of the table. Again we see that our symbols help out thought processes by emphasizing only the relevant information.

The truth tables for the other AND gates are shown below:

7400

| A | B | Y |

|---|---|---|

| L | L | H |

| L | H | L |

| H | L | L |

| H | H | L |

7402

| A | B | Y |

|---|---|---|

| L | L | H |

| L | H | L |

| H | L | L |

| H | H | L |

7410

| A | B | C | Y |

|---|---|---|---|

| L | L | L | H |

| L | L | H | H |

| L | H | L | H |

| H | L | L | H |

| H | H | L | L |

| H | H | H | H |

Note that the three input AND truth table has twice as many input combinations as the two input gates. This makes the truth table inconveniently long. As a result, truth tables are seldom used for gates with more than three inputs. How many input combinations are there for the 7430 gate?

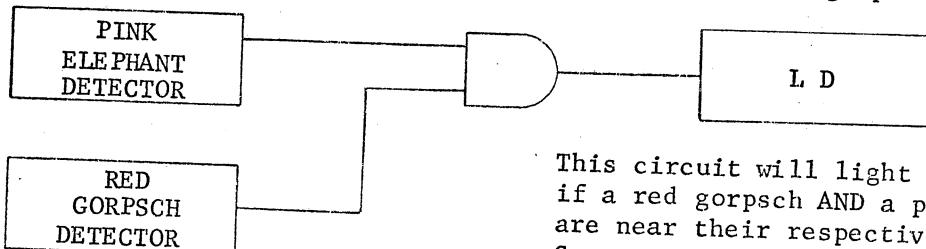

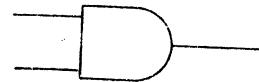

Now let us wire up some simple circuits. Assume we have two detectors and a lamp driver with the properties shown by their graphical symbols.

This circuit will light the lamp only if a red gorpisch AND a pink elephant are near their respective detectors.

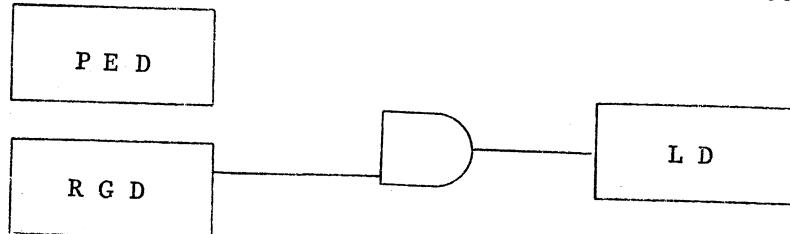

Suppose we want to modify the above circuit to light the lamp only if we

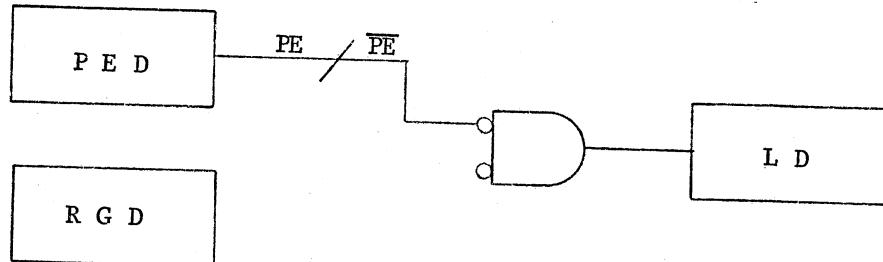

have a red gorpisch AND NOT a pink elephant. Go through the following thought processes:

- 1) We must have a logical AND. Choose a 7408 AND gate and draw it in the middle of the page.

2) The output polarity of the 7408 matches the input polarity of the lamp driver so they can be connected.

3) The output polarity of the red gorpisch detector matches the input polarity of the 7408 AND gate so these points can be connected.

4) We know we need a logical NOT operation on the output of the pink elephant detector. Draw it.

5) Now we need an inverter to change the polarity of  $\overline{PE}$  to the high required by the AND gate.

This completes the circuit.

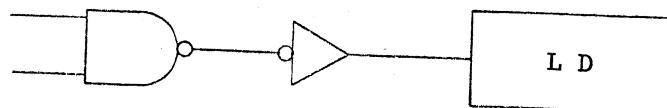

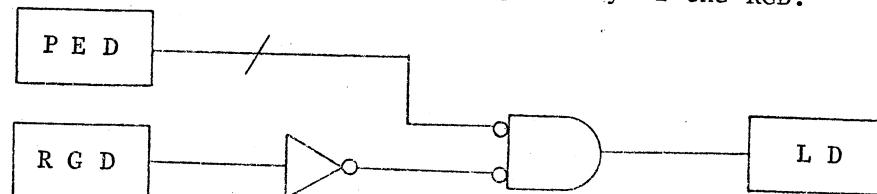

Let's repeat the above example using the 7400 AND gate.

1) Place the 7400 in the middle of the page.

2) The 7400 output doesn't match the input polarity of the lamp driver. It must be changed to the polarity expected by the lamp driver.

3) The rest of the circuit is identical to the first example. Let's repeat the above example using the 7402 AND gate.

a)

b) The output of the 7402 matches the input polarity of the lamp driver--connect them.

c) The output of the pink elephant detector has to have a slash to create  $\overline{PE}$ . The resulting polarity matches the input of the 7402.

d) The polarities of the RGD and the 7402 don't match so we must insert an inverter to change the polarity of the RGD.

THE BOOLEAN ALGEBRA OF THE AND GATE

There are several fundamental truths about the AND gate which can be neatly summarized by boolean algebra. This is the algebra of binary logic. In all of our previous work we have considered these two values to be H and L voltages. One can conceive of other digital logic systems where the variables are not voltages. An example would be a relay system where we are concerned with a relay contact being OPEN or CLOSED. Boolean algebra abstracts all binary systems by defining two logical variables 1 and 0. The boolean 1 and 0 can then represent H, L voltages or relay contacts being OPEN or CLOSED. A boolean 1 or 0 must not be confused with an ordinary numerical 1 or 0. Instead a boolean 1 is to be interpreted as a logical TRUE and a boolean 0 as a logical FALSE. We have already discussed how the correlation of TRUE and FALSE and voltages is to be made. An output or input with a circle is defined to be TRUE (boolean 1) for an L voltage. An output or input without a circle is defined to be a boolean 1 for an H voltage. The same convention holds for input polarities.

In terms of boolean variables the AND gate is defined by the following truth table:

| A | B | Y |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Each of the AND gates previously described has an identical boolean truth table when the input voltages are interpreted as boolean 1's or 0's according to the graphical symbol. Let us consider all of the two input AND gates and prove this statement for all of them.

| A | B | Y | A                      | B | Y |

|---|---|---|------------------------|---|---|

| L | L | L | 0                      | 0 | 0 |

| L | H | L | 0                      | 1 | 0 |

| H | L | L | (if 1=H,<br>for A,B,Y) | 1 | 0 |

| H | H | H |                        | 1 | 1 |

Since all of the inputs and outputs are non-circled, a boolean 1 is to be interpreted as an H voltage. If the above truth table is rewritten in terms of 1's and 0's the boolean AND truth table results.

| A | B | Y | (if 1=H<br>for A,B) | A | B | Y |

|---|---|---|---------------------|---|---|---|

| L | L | H |                     | 0 | 0 | 0 |

| L | H | H | =                   | 0 | 1 | 0 |

| H | L | H | (and 1=L<br>for Y)  | 1 | 0 | 0 |

| H | H | L |                     | 1 | 1 | 1 |

Rewrite this voltage truth table using an H = 1 for inputs A, B and L = 1 for Y. Again you get the standard truth table for the boolean AND.

The 7402 gate shown on the following page is left as an exercise for the reader.

Now for some boolean algebra. The important theorems are listed below:

$A \cdot B = B \cdot A$  Look at the truth table for the AND. The only case where  $A \cdot B$  could possibly be different from  $B \cdot A$  is if  $B$  was different from  $A$ . In other words  $A = 1$  and  $B = 0$ . From the truth table we see that  $1 \cdot 0 = 0$  and also  $0 \cdot 1 = 0$ , QED.

$1 \cdot 1 = 1$  Verify by looking at the last line of the truth table.

$1 \cdot 0 = 0$  Verify by looking at the middle lines of the truth table.

$A \cdot 1 = A$  if  $A = 0$ ,  $0 \cdot 1 = 0$

if  $A = 1$ ,  $1 \cdot 1 = 1$  QED

$A \cdot 0 = 0$  if  $A = 0$ ,  $0 \cdot 0 = 0$

if  $A = 1$ ,  $1 \cdot 0 = 0$  QED

$A \cdot A = A$  if  $A = 0$ ,  $0 \cdot 0 = 0$

if  $A = 1$ ,  $1 \cdot 1 = 1$  QED

The last theorem requires a result from a logical NOT operation. The boolean algebra of the NOT operation is so simple it was not covered in that chapter. These results are:

$$\begin{aligned}\overline{1} &= 0 \\ \overline{0} &= 1\end{aligned}$$

Now we can state the final theorem on the AND.

$A \cdot \overline{A} = 0$  if  $A = 1$ ,  $A \cdot \overline{A} = 1 \cdot 0 = 0$

if  $A = 0$ ,  $A \cdot \overline{A} = 0 \cdot 1 = 0$  QED

The power of boolean algebra is it allows us to formulate these general results independently from the particular type of logic we are discussing. Although these results are very simple you should memorize them since they will form the basis of some gate simplifications later on.

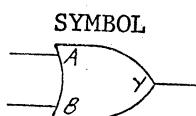

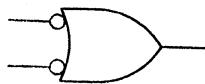

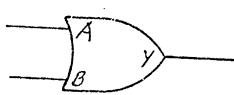

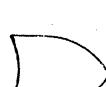

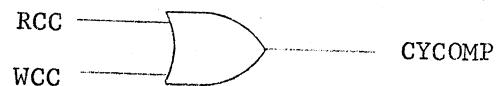

The definition of the logical OR is:

THE OUTPUT WILL BE TRUE IF AT LEAST ONE OF THE INPUTS IS TRUE.

Again the definition of true can be obtained from the symbol for the OR gate. Small circles correspond to L voltages.

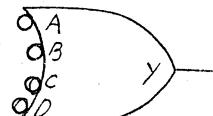

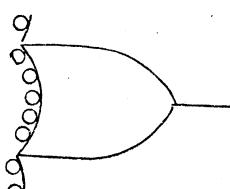

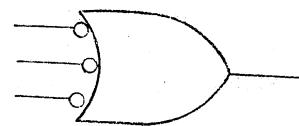

The common OR gates and their IC catalog numbers are:

| NAME            | SYMBOL                                                                              | CAT. # | BEHAVIOR                                                |

|-----------------|-------------------------------------------------------------------------------------|--------|---------------------------------------------------------|

| 2 input OR gate |    | 7432   | Y will be H if A OR B (or both) is H                    |

| 2 input OR gate |    | 7408   | Y will be L if one OR more of A, B is L                 |

| 2 input OR gate |    | 7400   | Y will be H if one OR more of A, B is L                 |

| 3 input OR gate |   | 7410   | Y will be H if one OR more of A, B, C is L              |

| 4 input OR gate |  | 7420   | Y will be H if one OR more of A, B, C, D is L           |

| 8 input OR gate |  | 7430   | the output will be H if one OR more of the inputs are L |

As for the AND gate we can write a truth table for the OR gate. The truth table is an equivalent way of defining the device. Consider the 7432

| A | B | Y |

|---|---|---|

| L | L | L |

| L | H | H |

| H | L | H |

| H | H | H |

Note that the symbol emphasizes the last three rows of the truth table. This says the output will be true if either OR both the inputs are true. The first row is implied by the symbol but if you are designing actual hardware and need an OR gate you are not explicitly concerned with the first row.

The truth table for the 7400 is:

| A | B | Y |

|---|---|---|

| L | L | H |

| L | H | H |

| H | L | H |

| H | H | L |

In this case the symbol emphasizes the first three rows of the truth table. It is just these three rows that embody the logical OR function for this device.

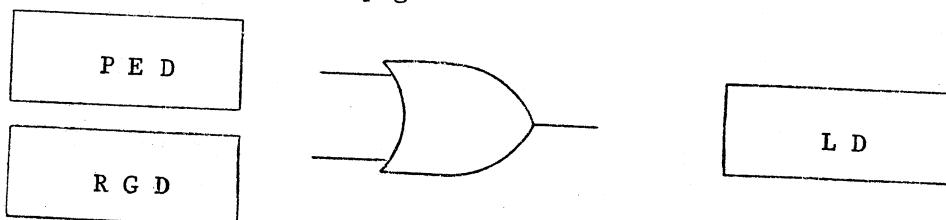

Let us consider some simple examples using OR gates:

Draw a circuit using a 7432 gate that will light a lamp when I have either a red gorpisch OR a pink elephant.

1) Since the OR gate is the central part of the problem draw it in the middle of the page

2) Since all polarities match all connections can be made directly.

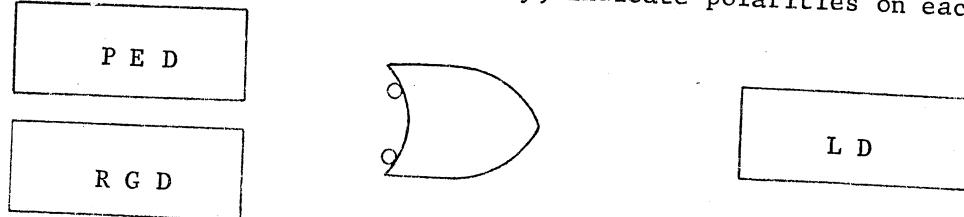

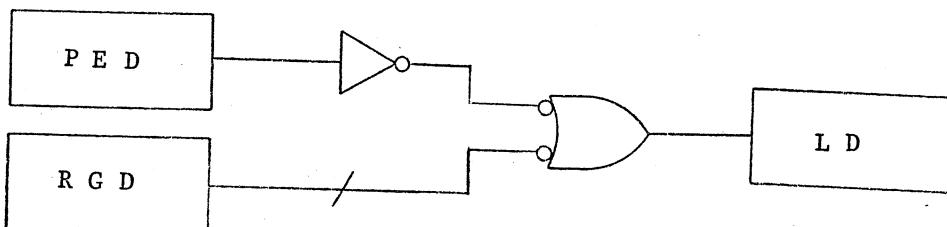

Draw a circuit using a 7400 gate that will light a lamp when we have either NOT a red gorpisch OR a pink elephant.

1) Lay out the circuit graphically, indicate polarities on each symbol.

2) The polarities of the 7400 output and lamp driver match--connect them.

3) The polarities of the pink elephant detector and the input of the 7400 don't match. Insert an inverter to "match up" the polarity.

4) Take care of the NOT operation on the red gorpisch line. This means a slash must be put on the output line from the red gorpisch detector. Remember the meaning of the slash--polarities must differ on either side of the slash. This is already true so a director connection can be made.

Build the same circuit using the 7402.

#### THE BOOLEAN ALGEBRA OF THE OR GATE.

The boolean definition of the OR gate is shown by the following truth table:

| A | B | Y |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Each of the OR gates described previously has an identical boolean truth table when the input and output voltages are interpreted as boolean 1's and 0's according to the symbol. Let us prove this for the two input gates.

| A | B | Y | input 1=H  | A | B | Y |

|---|---|---|------------|---|---|---|

| L | L | L |            | 0 | 0 | 0 |

| L | H | H |            | 0 | 1 | 1 |

| H | L | H |            | 1 | 0 | 1 |

| H | H | H | output 1=H | 1 | 1 | 1 |

| A | B | Y | input 1=L  | A | B | Y |

|---|---|---|------------|---|---|---|

| L | L | H |            | 1 | 1 | 1 |

| L | H | H |            | 1 | 0 | 1 |

| H | L | H |            | 0 | 1 | 1 |

| H | H | L | output 1=L | 0 | 0 | 0 |

Note that the order of the lines in the boolean truth table has been scrambled from the formal definition given above. This of course does not matter since the output depends only on the input combinations.

| A | B | Y | input 1=H  | A | B | Y |

|---|---|---|------------|---|---|---|

| L | L | H |            | 0 | 0 | 0 |

| L | H | L |            | 0 | 1 | 1 |

| H | L | L |            | 1 | 0 | 1 |

| H | H | L | output 1=L | 1 | 1 | 1 |

The student should do the same exercise for the 7408 OR gate.

Let us consider some boolean algebra for the OR gate. The symbol for the boolean OR is a  $+$ . This should not be confused with the arithmetic plus. Since in digital logic we deal far more often with the OR than with the plus we give plus a special symbol  $(+)$ . Thus:

$A + B$  means  $A$  OR  $B$

$A (+) B$  means arithmetic sum of  $A$  and  $B$

The theorems for the OR are listed below:

$A + B = B + A$  This can be verified by looking at the truth table defining the logical OR

$0 + 0 = 0$  First line of defining truth table.

$1 + 0 = 1$  Second and third lines of defining truth table.

$A + 0 = A$  if  $A = 0$ ,  $0 + 0 = 0$

if  $A = 1$ ,  $1 + 0 = 1$  QED

$A + 1 = 1$  if  $A = 0$ ,  $0 + 1 = 1$

if  $A = 1$ ,  $1 + 1 = 1$  QED

$A + A = A$  if  $A = 0$ ,  $0 + 0 = 0$

if  $A = 1$ ,  $1 + 1 = 1$  QED

$A + \bar{A} = 1$  if  $A = 0$ ,  $0 + 1 = 1$

if  $A = 1$ ,  $1 + 0 = 1$  QED

DeMorgan's theorems: These are two very important theorems which you will use so often they will become automatic. In each case we will prove them by means of truth tables which is not the most sophisticated proof but is the simplest. Further it will give you more experience handling boolean truth tables.

THEOREM 1:

$$\overline{A \cdot B} = \overline{A} + \overline{B}$$

PROOF

- Form the truth table for  $A \cdot B$ .

- Complement the column  $\overline{A \cdot B}$  to obtain the left side of the above equation.

Note that complement is another name for the logical NOT. Note that  $\overline{A \cdot B} \neq \overline{A} \cdot \overline{B}$  which you should prove by filling in the truth table for  $A \cdot \overline{B}$ .

| A | B | $A \cdot B$ | $\overline{A \cdot B}$ |

|---|---|-------------|------------------------|

| 0 | 0 | 0           | 1                      |

| 0 | 1 | 0           | 1                      |

| 1 | 0 | 0           | 1                      |

| 1 | 1 | 1           | 0                      |

- Form the truth table for  $\overline{A} + \overline{B}$  and compare with b).

| A | B | $\overline{A}$ | $\overline{B}$ | $\overline{A} + \overline{B}$ |

|---|---|----------------|----------------|-------------------------------|

| 0 | 0 | 1              | 1              | 1                             |

| 0 | 1 | 1              | 0              | 1                             |

| 1 | 0 | 0              | 1              | 1                             |

| 1 | 1 | 0              | 0              | 0                             |

The last columns of b) and c) agree; therefore we have proved DeMorgan's First Theorem.

THEOREM 2:

$$\overline{A + B} = \overline{A} \cdot \overline{B}$$

The proof proceeds in the same fashion.

| A | B | $\overline{A}$ | $\overline{B}$ | $A + B$ | $\overline{A + B}$ | $\overline{A} \cdot \overline{B}$ |

|---|---|----------------|----------------|---------|--------------------|-----------------------------------|

| 0 | 0 | 1              | 1              | 0       | 1                  | 1                                 |

| 0 | 1 | 1              | 0              | 1       | 0                  | 0                                 |

| 1 | 0 | 0              | 1              | 1       | 0                  | 0                                 |

| 1 | 1 | 0              | 0              | 1       | 0                  | 0                                 |

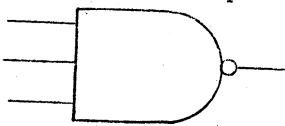

What relationship do DeMorgan's theorems have to AND, OR gates? Said in words the theorems say:

IF ALL INPUTS AND OUTPUTS ARE INVERTED, AND and OR WILL BE INTERCHANGED.

Symbolically:

$\equiv$

$\equiv$

This is true as we'll show by using voltage truth tables:

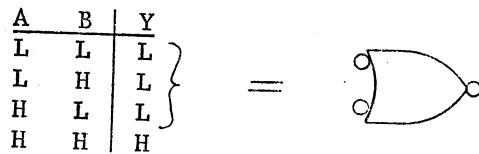

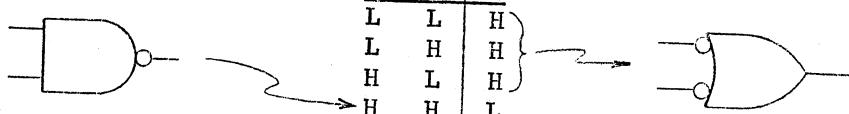

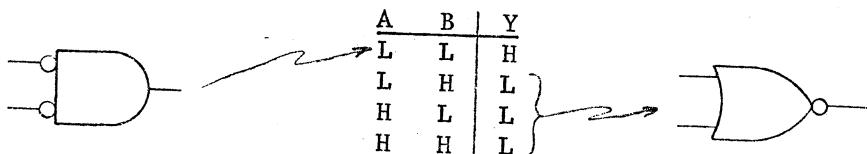

The AND symbol emphasizes the last line of the truth table (the AND line) and implies the other three lines.

Now let us take the first three lines of the same voltage truth table (the OR lines) and represent their behavior with a graphical symbol.

We see that the AND and OR symbol emphasize different parts of the same truth table. Of course either symbol implies the entire truth table. Still as designers we will be thinking of AND or OR functions. YOUR SYMBOLS SHOULD REPRESENT THE TYPE OF GATE (AND or OR) THAT YOU WERE THINKING OF WHEN YOU DESIGNED THE CIRCUIT. THE SYMBOLS WILL IN TURN INDICATE THE POLARITY REQUIRED TO MAKE THEM ACT THE WAY THEY ARE DRAWN.

This concept is so important that we will illustrate it for all of the commercially available two input gates.

CAT. #

SYMBOL

VOLTAGE TRUTH TABLE

EQUIVALENT SYMBOL

7400

7402

7408

7432

THUS WE CAN USE ONE AND THE SAME GATE AS A LOGICAL AND or A LOGICAL OR BY GIVING IT INPUTS OF THE PROPER POLARITY!

This is not restricted to two input gates. For example the 7410 can be represented in two equivalent forms.

The student must learn to "change gears" automatically when thinking of AND or OR gates, since this will allow you to simplify circuits.

As you have seen we have devised a very nice graphical way of representing digital logic circuits. The pictures tell us what operations (NOT, AND, OR) are taking place and also what polarities are at any point in the circuit. This pictorial representation called a LOGIC DIAGRAM is the most useful way of portraying a circuit that is already built.

Unfortunately it is a rather cumbersome way to do the initial design of a circuit. A more compact way to represent the boolean operations is required. This information can be represented by boolean equations. Again we will find that they are tailored to certain applications. They are useful precisely because they emphasize certain things and suppress irrelevant items. One thing suppressed is voltage polarity. Indeed, from a preliminary design viewpoint we are interested in implementing AND's, OR's, NOT's, etc., and are not concerned with polarities. Of course when it comes time to build or debug a circuit then polarities are all important. At that point a logic diagram will be needed. This chapter will be devoted to translating logic equations to logic diagrams.

The symbols used to write equations are divided into two classes:

**Variables:** These are simply the names of signals. Examples would be: A, A39, AC LOAD. A superficially more complex name would be AC=0. Such a name tells you the condition that will make the line true. For AC=0 it would be true only if all bits in the accumulator were = 0. Note the = sign is part of the name in this case.

**Operators:**

|          |                                                                  |

|----------|------------------------------------------------------------------|

| .        | logical AND                                                      |

| +        | logical OR                                                       |

| <u>-</u> | logical NOT (this is an overscore)                               |

| ( )      | parenthesis (used as in ordinary algebra)                        |

| =        | equals (used as in ordinary algebra unless it is part of a name) |

Let us consider some simple examples:

$$F = A \cdot B$$

An equivalent way of representing the same information would be a logical truth table:

| A | B | F |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

If you want to build a logic circuit to generate F you must provide two additional pieces of information:

- What type of AND gate you will choose from the IC catalog

- What polarities A, B, and F will be represented by.

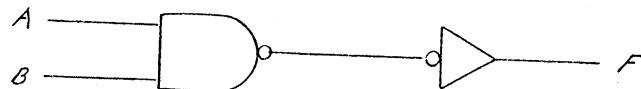

Suppose the gate is a 7400 and TRUE for A, B, F is represented by H. Now the circuit can be drawn

Another example:

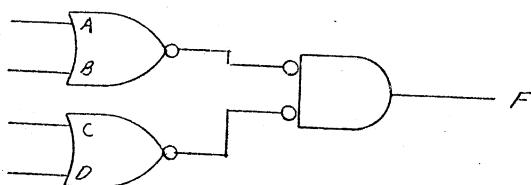

$$F = (A + B) \cdot (C + D)$$

The parenthesis tells us that  $A + B$  must be generated as an intermediate signal, as must  $C + D$ . Then these two intermediate signals must be ANDed. Again suppose F, A, B, C, D are all TRUE when H. Also suppose the 7402 is chosen for the gates. All three gates are 7402's. We have used

DeMorgan's theorem to represent the same gate in its most natural form at each place in the circuit.

Such simple examples do not really express the power of boolean equations. Before we can go to more realistic examples it is necessary to consider the implied priority of the different operators. Consider:

$$F = A \cdot B + C$$

This could mean:

$$F = A \cdot (B + C)$$

(+ has more priority than ·)

(· has more priority than +)

The proper interpretation is the second. We can formalize this in a table of priorities (hierarchies) the most "powerful" operator being at the left:

| NOT | AND | OR |

|-----|-----|----|

| ( ) | ·   | +  |

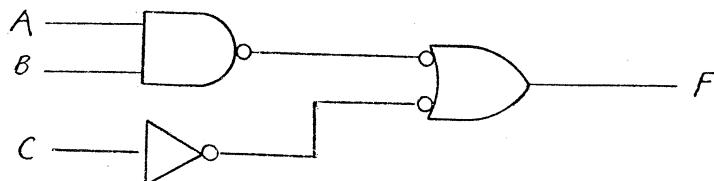

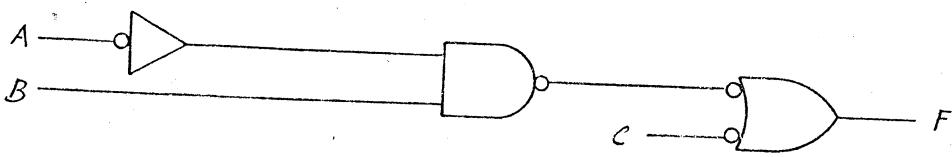

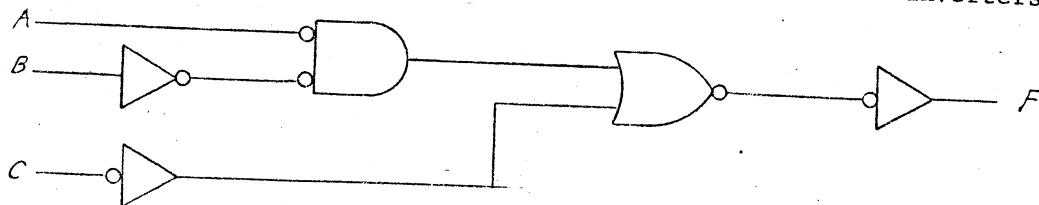

Let us now derive a circuit that will generate  $F = A \cdot B + C$  where TRUE is represented by H and we choose 7400 gates for implementation.

Let us implement  $F = A \cdot B + C$  where TRUE for each variable is defined by  $F = H$ ,  $A = L$ ,  $B = H$ ,  $C = L$ .

Again let us choose 7400 gates for implementation.

This logic diagram looks very different from the preceding one. Yet, it is the same boolean equation that is being implemented. The difference is caused by the differing polarities chosen to represent TRUE. Still another factor that could change the appearance would be to choose a different gate to implement the circuit. Suppose that 7402's were chosen and the polarities are the same. We see that it takes two more inverters to implement the same boolean equation. It is generally true that one type of gate will be more "natural" for a given situation. The designer should exploit this by choosing the type of gate which minimizes the number of inverters.

Logic equations can also be used to state general theorems. A few of these theorems should be memorized since they will allow you to build circuits with fewer gates.

The important theorems are listed below:

|                       |                           |

|-----------------------|---------------------------|

| 1a) $A + 0 = A$       | 1b) $A \cdot 1 = A$       |

| 2a) $A + 1 = 1$       | 2b) $A \cdot 0 = 0$       |

| 3a) $A + A = A$       | 3b) $A \cdot A = A$       |

| 4a) $A + \bar{A} = 1$ | 4b) $A \cdot \bar{A} = 0$ |

These theorems have already been discussed in the chapters on the logical AND and OR. They should be at your fingertips since it is unfor-givable to convert one of these equations to gate form.

$$5a) A(A + B) = A \quad 5b) A + AB = A$$

Note that when two single letter variables such as A, B are written side by side the AND is implied thus  $AB = A \cdot B$ . This is true only if the variables are named by single letters.

These boolean identities can be proved by truth tables. For example 5a):

We see that the columns for A and  $A \cdot (A + B)$  match QED.

| A | B | $A+B$ | $A(A+B)$ |

|---|---|-------|----------|

| 0 | 0 | 0     | 0        |

| 0 | 1 | 1     | 0        |

| 1 | 0 | 1     | 1        |

| 1 | 1 | 1     | 1        |

5b): Alternatively they could be proved using boolean algebra. For example

$$A + AB = A(1 + B) = A \cdot (1) = A$$

$$6a) A(\bar{A} + B) = AB \quad 6b) A + \bar{A}B = A + B$$

6a) is easy to prove using boolean algebra:

$$A(\bar{A} + B) = A\bar{A} + AB = 0 + AB = AB$$

$$7a) \bar{AB} = \bar{A} + \bar{B} \quad 7b) \overline{A + B} = \bar{A} \cdot \bar{B}$$

These are simply DeMorgan's theorems.

$$8a) AB + A\bar{B} = A$$

This is an important theorem which is the basis of the Karnaugh Map simplification. Its proof is simple:  $AB + A\bar{B} = A(B + \bar{B}) = A \cdot (1) = A$ .

The human mind works best when irrelevant material can be suppressed. We have already seen how each of our various ways of representing digital logic emphasizes certain things and de-emphasizes others. Consequently, we use the description that best suits the task at hand.

The next step up this ladder is to combine gates into useful structures. Once we do this we can give this structure a name. Once named the human mind can then use the new structure easily. We will describe and name most of the common items used in computer architecture.

#### A) EXCLUSIVE OR

This is a logic function of two inputs and one output. The definition can be given either by a truth table or a boolean equation. We will do both, but we must first give it a boolean operator symbol which is  $\oplus$ .

which is equivalent to

$A \oplus B = A\bar{B} + \bar{A}B$

| A | B | $A \oplus B$ |

|---|---|--------------|

| 0 | 0 | 0            |

| 0 | 1 | 1            |

| 1 | 0 | 1            |

| 1 | 1 | 0            |

From the truth table we can see that it is identical to the logical OR except it excludes the case  $A = B = 1$ .

The exclusive OR is used enough to warrant its production as a special integrated circuit, the 7486. The graphical symbol is modified from the normal symbol of the logical OR: Note also that it has only two inputs.

a) Use as a controlled inverter: This technique should be in every designer's bag of tricks, especially since it is so simple. Suppose we wish to pass a signal (A) unchanged when a control signal (C) is 0 and invert A when the control signal is 1.

This is the exclusive OR definition as we can show from the truth table:

|          |                        | C | A | $A \oplus C$ |

|----------|------------------------|---|---|--------------|

| when C=0 | $A \oplus C = A$       | 0 | 0 | 0            |

| when C=1 | $A \oplus C = \bar{A}$ | 0 | 1 | 1            |

|          |                        | 1 | 0 | 1            |

|          |                        | 1 | 1 | 0            |

b) Use as a comparator: Look at the truth table again and you will notice that the output of  $A \oplus B$  is a 1 only when  $A \neq B$ . Therefore, all we have to do to see if both bits are the same is take the logical NOT of the output.

(L only when A = B)

c) Use as a parity generator/checker: Parity is a reliability feature that is used on most computers. The philosophy behind it is to try to give an automatic warning when some component of the computer fails. One common device that is parity checked is memory. The common failure mode of memory is that one bit will always come back a 0, the other failure mode is for it to always come back a 1. Some examples are:

| INPUT                      | OUTPUT                                    |

|----------------------------|-------------------------------------------|

| good memory 0011 1010 0001 | 0011 1010 0001                            |

| bad memory 0011 1010 0001  | 0011 1010 0000<br>(last bit<br>always 0)  |

| bad memory 0011 1010 0001  | 1011 1010 0001<br>(first bit<br>always 1) |

Of course with a good memory you will always read back what you stored. When the memory goes bad you will either "PICK UP" or "DROP" a bit. How could you check for this? Consider the original word stored in memory 0011 1010 0001; it has 5 bits = 1. Note that 5 is an ODD number. If the last bit is dropped the number returned from memory will be 0011 1010 0000 which has 4 bits = 1 which is an EVEN number. If a bit is picked up, i.e., 1011 1010 0001, 6 bits = 1, which is STILL an even number. Thus a bit pickup or drop causes the number of bits to change from ODD to EVEN.

SUCH AN ERROR IS CALLED A PARITY ERROR.

Of course we will not always be storing numbers with an odd number of bits; for example we might store 0010 0011 1000 which has 4 bits = 1 (EVEN), and a bit pick up or drop will result in

a number with an ODD number of 1's which is still a parity error. How do you distinguish these cases? You append an extra bit (the parity bit) to the original number so the total number of bits (including the parity bit) is odd. For example:

1) 0011 1010 0001 is already ODD      parity bit = 0

final number is 0 0011 1010 0001      total bits = 1 is ODD

parity bit      original number

2) 0010 0011 1000 has an even number of 1 bits; therefore

the parity bit = 1

final number is 1 0010 0011 1000      total bits = 1 is ODD

parity bit      original number

Now let us send these 13 bit numbers to a faulty memory. The parity bit has been appended so that the number of 1 bits is always odd. Now a bit drop or pickup will always result in an even number of 1 bits.

If we had some way of looking at a number and telling whether it had an odd number of bits we could build a circuit that would detect a parity error.

Look at the exclusive OR truth table again. It has two input bits. Its output is a 1 only if the number of 1 bits in the input is ODD.

| A | B | $A \oplus B$ |

|---|---|--------------|

| 0 | 0 | 0            |

| 0 | 1 | 1            |

| 1 | 0 | 1            |

| 1 | 1 | 0            |

only 1 bit of A or B is

= 1 (1 is an odd number)

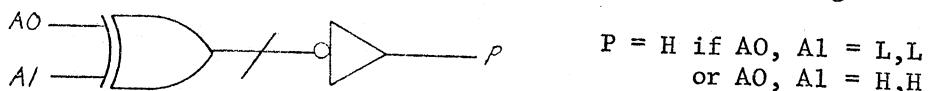

Thus if we have a 2 bit number (A<sub>0</sub>, A<sub>1</sub>), we can calculate the parity bit to append to it (P, A<sub>0</sub>, A<sub>1</sub>) with the following circuit.

$$P = H \text{ if } A_0, A_1 = L, L \text{ or } A_0, A_1 = H, H$$

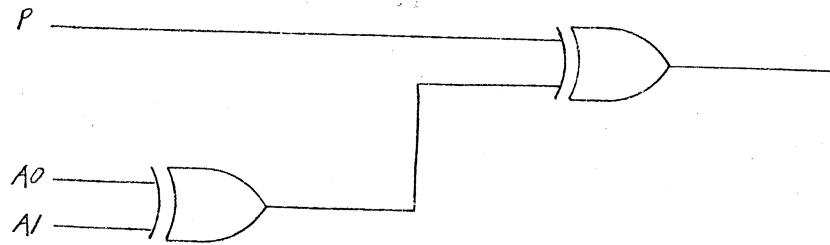

We can ship this modified number P, A<sub>0</sub>, A<sub>1</sub> to a faulty memory which may be picking up or dropping a bit. How do we tell? We take the number we get back from memory and use exclusive OR's to see if it still has an ODD number of bits. If yes, we did not have a parity error. The circuit to check this is shown below:

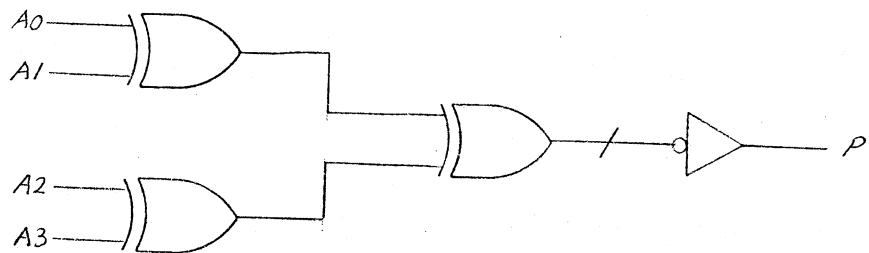

This is a very simple parity checking circuit in that the original number  $A_0, A_1$  was only 2 bits. A more typical width would be the word size of the computer. For the PDP-8 this is 12 bits. How would you generate the parity bit to append to the 12 bit word? Hint: shown below is the circuit to generate the parity bit for a 4 bit word.

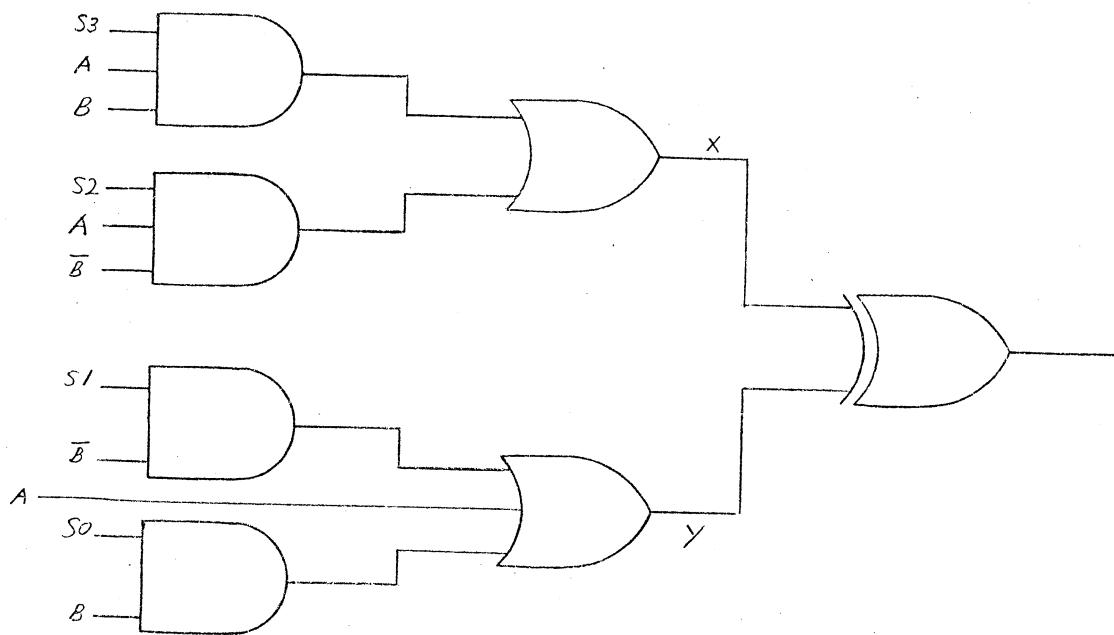

### B) THE MULTIPLEXOR (DATA SELECTOR)

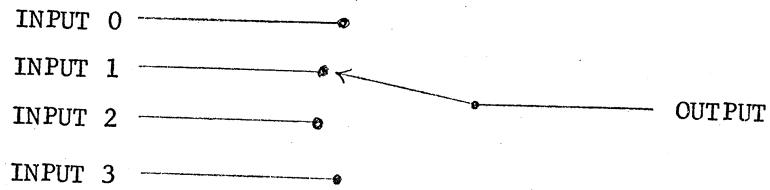

The data selector (often abbreviated MUX) is essentially an electronically controlled switch. Its function is to take many inputs, select only one of them, and route the selected one to the output. It is exactly analogous to a mechanical rotary switch as shown below:

With a manual switch the position is controlled by a knob. MUX's act like the rotary switch but are made of AND, and OR gates. This makes the selection process very fast since gates switch in just a few nano seconds. There are either 1, 2, 3, or 4 switch selection lines in IC MUX's. Therefore, there can be  $2^1 = 2$ ,  $2^2 = 4$ ,  $2^3 = 8$ , or  $2^4 = 16$  different inputs. We will describe these in turn:

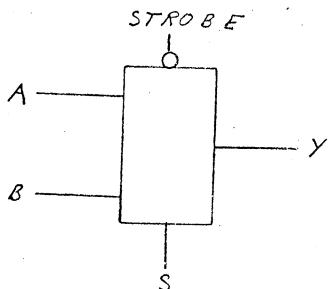

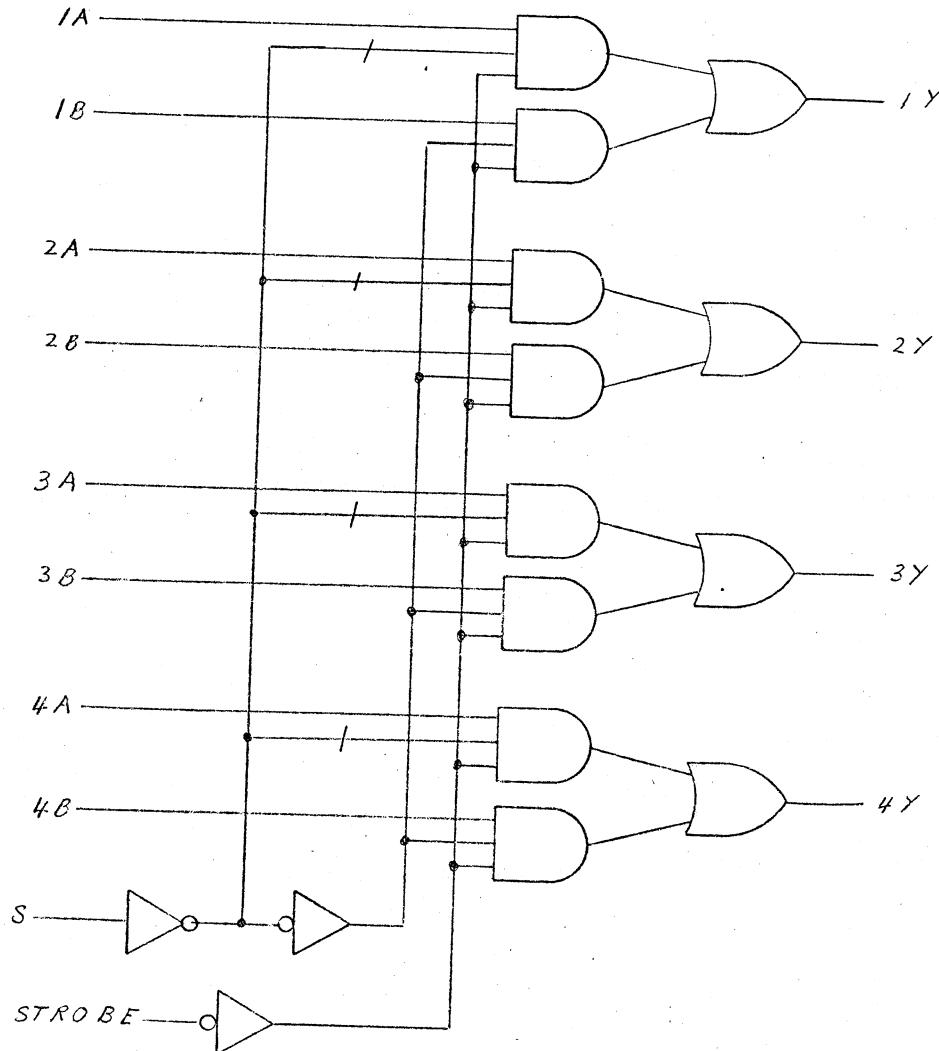

## 1) 2 INPUT MUX catalog number 74157

Since it is a special purpose circuit its symbol is a rectangle. A, B are inputs which can be switched to Y by means of the control line S. The strobe line is also important; unless it is L none of the inputs are connected to Y. All of the following discussion assumes strobe = L.

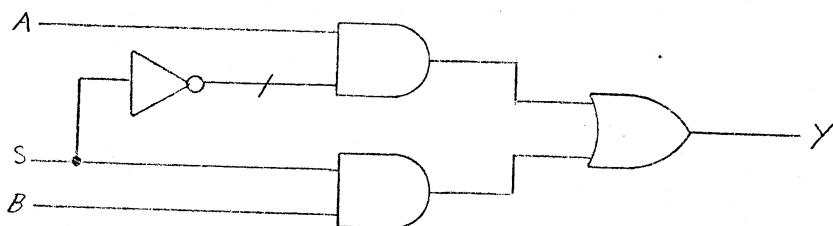

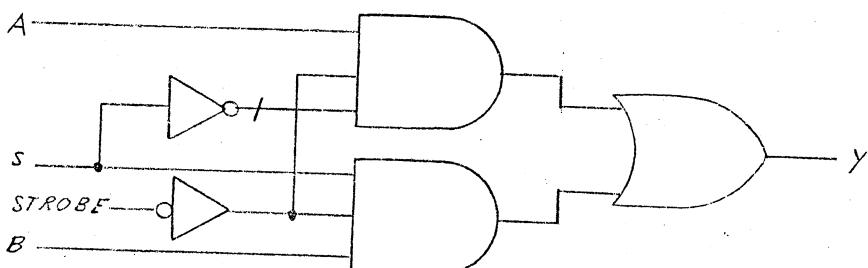

When S = L, A is connected to Y. When S = H, B is connected to Y. For the moment ignore strobe; what combination of AND, OR gates would implement this circuit?

Convince yourself that this circuit does indeed duplicate the above description. How can we implement STROBE? (Remember when strobe = H, all inputs are disconnected from Y).

To get the actual circuit for the 74157 we have to consider one obscure fact. Each gate input absorbs some electrical power. There are four identical two input MUX's per IC package. If we simply took four of the previous circuits and hooked all four select (S) lines to the same pin we would draw four times as much power from the gate which generated the S signal elsewhere in our computer. This would LOAD that gate excessively.

Therefore, we use two inverters on the S line. We take our select signals off of these outputs. Now we draw only one unit of power from the gate which is generating S.

Several comments are in order:

- AND, OR gates don't look anything like a rotary switch but they will simulate it, and much faster too.

- You buy four of these switches per IC package at a cost of roughly \$1.50.

- It is much easier to think of a MUX than the gates inside the MUX. After all in a computer we are going to have to route information inside the machine. Even though this is done by gates they clutter up the picture.

d) We could have described the MUX by means of equations, i.e.,  $Y = A \cdot \text{STROBE} \cdot S + B \cdot \text{STROBE} \cdot \bar{S}$ .

e) We could have described the device by means of a truth table:

|                                   | STROBE | S | A | B | Y |

|-----------------------------------|--------|---|---|---|---|

| Note the use<br>of X              | H      | X | X | X | L |

| X = irrelevant,<br>that is H or L | L      | L | L | X | L |

|                                   | L      | L | H | X | H |

|                                   | L      | H | X | L | L |

|                                   | L      | H | X | H | H |

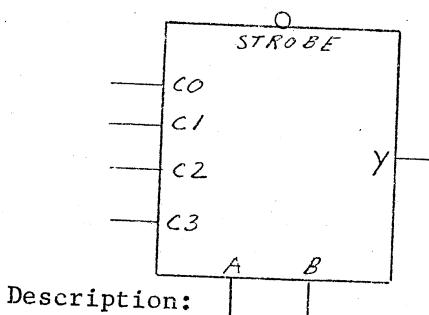

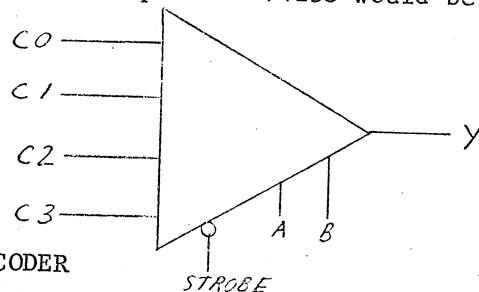

2) 4 input MUX catalog number 74153

NOTE: the four inputs are called C0-C3. The select lines are now called A, B. Strobe has the same meaning as before.

Description:

a)  $Y = (C0 \cdot \bar{A} \cdot \bar{B} + C1 \cdot \bar{B} \cdot A + C2 \cdot B \cdot \bar{A} + C3 \cdot B \cdot A) \cdot \text{STROBE}$

b) Truth table

| STROBE | B | A | C0 | C1 | C2 | C3 | Y |

|--------|---|---|----|----|----|----|---|

| H      | X | X | X  | X  | X  | X  | L |

| L      | L | L | L  | X  | X  | X  | L |

| L      | L | L | H  | X  | X  | X  | H |

| L      | L | H | X  | L  | X  | X  | L |

| L      | L | H | X  | H  | X  | X  | L |

| L      | H | L | X  | X  | L  | X  | L |

| L      | H | L | X  | X  | H  | X  | H |

| L      | H | H | X  | X  | X  | L  | L |

| L      | H | H | X  | X  | X  | H  | H |

c) As an exercise draw a logic diagram using AND, OR gates that implements a, b above

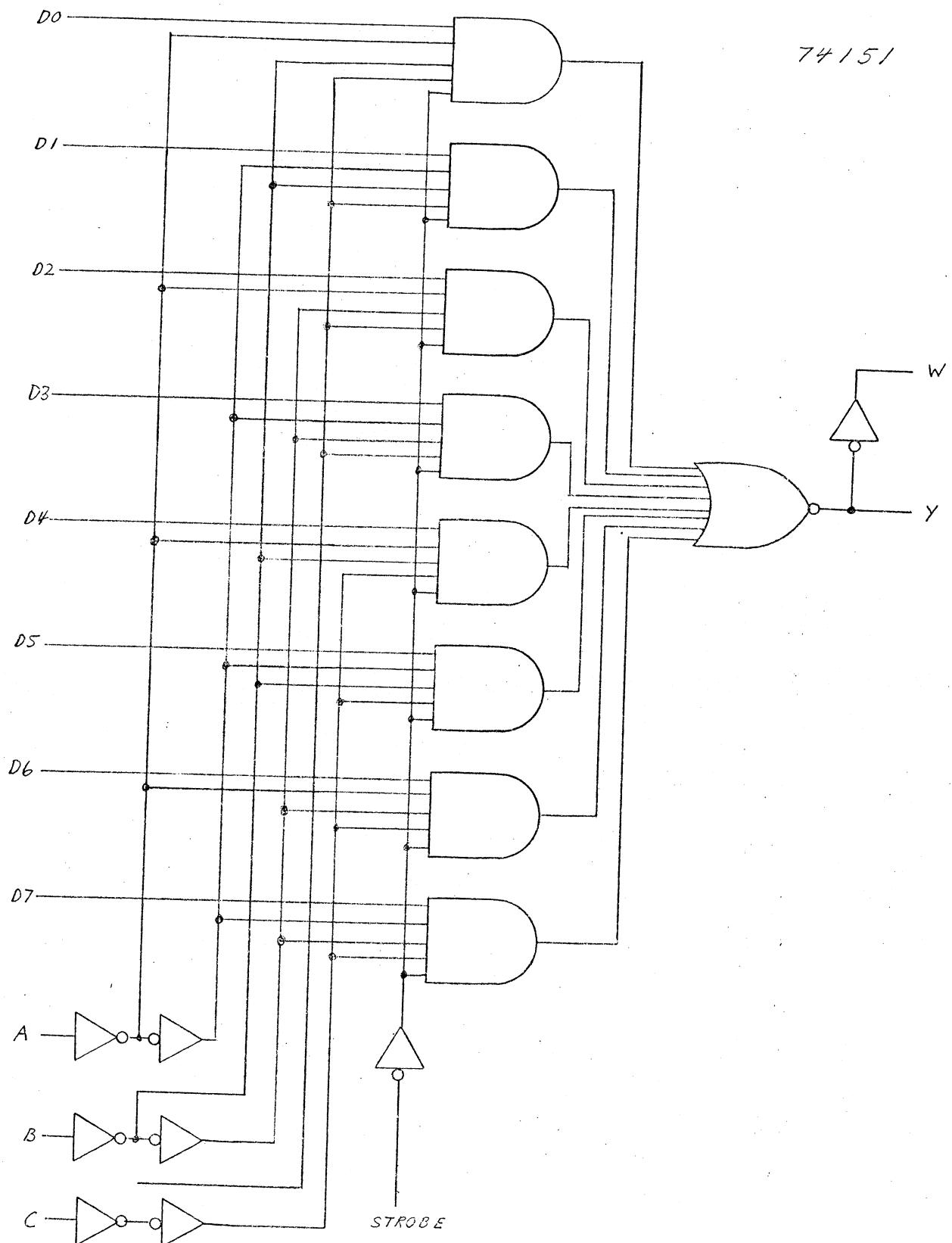

3) 8 input MUX catalog number 74151

4) 16 input MUX catalog number 74150

These are identical devices to 1 and 2 except for the increased number of inputs. Figure 6.1 is the logic diagram of the 74151 MUX.

Fig. 6.1

NOTE: Y outputs are circled on 150, 151

Y outputs are uncircled on 153, 157

W output on 151

One last point: Some authors use a triangle to represent a MUX. For example the 74153 would be shown as:

c) THE DECODER

Often we will have to look at a collection of bits and pick out a certain combination. For example in the laboratory computer project the left three bits of a command word tell what kind of instruction it is. Let us label this three bit field IRO, IR1, IR2. The possible combinations and their meanings are:

| IRO | IR1 | IR2 | INSTRUCTION                          |

|-----|-----|-----|--------------------------------------|

| 0   | 0   | 0   | AND accumulator and memory           |

| 0   | 0   | 1   | TAD accumulator and memory           |

| 0   | 1   | 0   | ISZ increment and skip if zero       |

| 0   | 1   | 1   | DCA store and clear accumulator      |

| 1   | 0   | 0   | JMS jump to subroutine               |

| 1   | 0   | 1   | JMP jump                             |

| 1   | 1   | 0   | IØ input output instruction          |

| 1   | 1   | 1   | NMR non-memory reference instruction |

Now the question is how do we tell when we have a given instruction? This can be most easily shown by a boolean equation. For example:

$NMR = IRO \cdot IR1 \cdot IR2$  since NMR is the only instruction with all bits TRUE.

Satisfy yourself that each of the following equations is correct:

$$IØ = IRO \cdot \overline{IR1} \cdot \overline{IR2}$$

$$JMP = IRO \cdot \overline{IR1} \cdot IR2$$

$$JMS = IRO \cdot \overline{IR1} \cdot \overline{IR2}$$

$$DCA = \overline{IRO} \cdot IR1 \cdot IR2$$

$$ISZ = \overline{IRO} \cdot \overline{IR1} \cdot \overline{IR2}$$

$$TAD = \overline{IRO} \cdot \overline{IR1} \cdot IR2$$

$$AND = \overline{IRO} \cdot \overline{IR1} \cdot \overline{IR2}$$

This process is called instruction decoding and the circuits to accomplish it are called decoders.

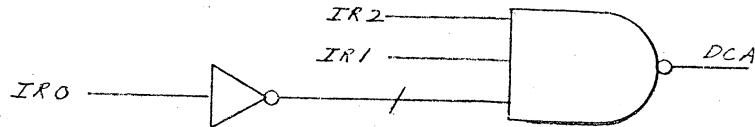

Let us build a decoder to detect the presence of the DCA instruction. Assume that IRO, IR1, IR2 are TRUE when H and DCA will be true when L.

$$DCA = \overline{IRO} \cdot IR1 \cdot IR2$$

$$For JMS = IRO \cdot \overline{IR1} \cdot \overline{IR2}$$

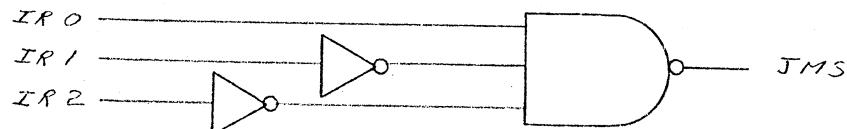

Decoding all eight instructions would take six more circuits analogous to the two above. The integrated circuit manufacturers have been nice enough to package all eight of these circuits into one IC.

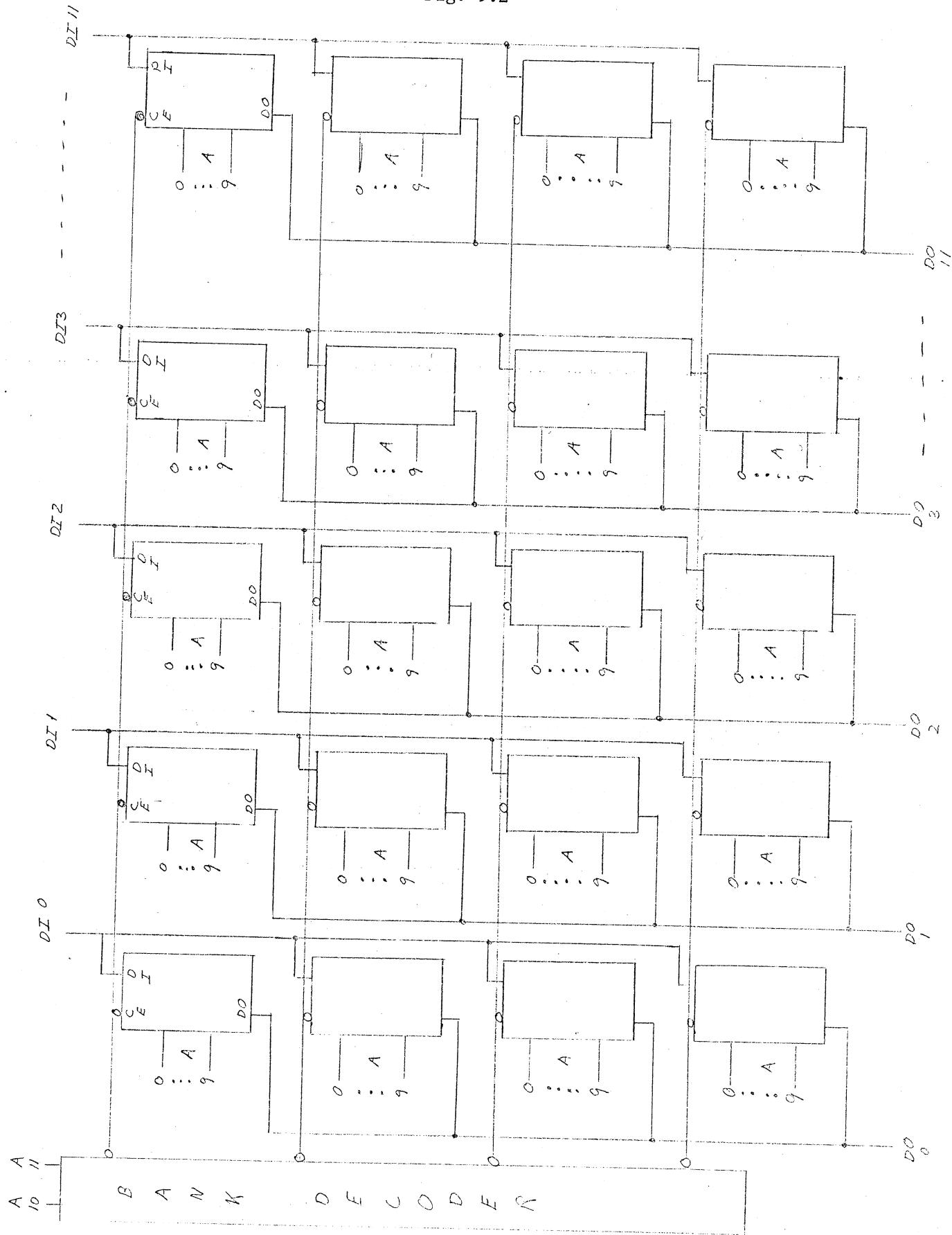

The most common decoders (and therefore the cheapest) are the 7442, which decode 10 outputs and the 74154 which decode 16 outputs. Both are used in your lab kit. A schematic of the 7442 is shown on figure 6.2. The schematic of the 74154 is identical except it has six more gates to decode the input combinations from 1010 - 1111. It also has a pair of enable terminals which must both be low to activate the decoder.

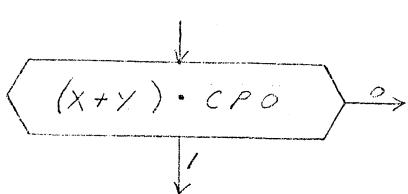

The enable capability of a decoder is very important. For example we discussed the use of a decoder to generate a unique signal for every command. It should be intuitively obvious that we would want to look at these signals only during the execution portion of a computer cycle. In other words we want to enable the instruction decoder only during the execute cycle.

At first sight the 7442 does not have this capability. However, if we choose to look at the first eight outputs only, then the D input will serve as an enable. You can see this by examining the decode gates for outputs 0 - 7. Every one of these gates has a  $\overline{D}$  input. Thus they will be enabled only if  $D = 0$ .

The student should look in a commercial IC catalog (such as the Texas Instruments TTL data book) for the logic diagram of the 74154.

There is one more very important combinatorial circuit, the binary adder. To allow adequate space for its discussion we have devoted the entire next chapter to it.

Fig. 6.2

42

## (7) ADDITION

A computer that can't add obviously isn't worth much. It is fairly easy to build a combinatorial circuit to add binary numbers. This chapter is devoted to a slow and easy introduction to the process and will culminate in an actual circuit that will add two numbers.

In the introduction we saw how a decimal number can be represented using only 0's and 1's. We call the resulting representation a binary number. To refresh your memory we will give the binary representation of several numbers:

$$5_{10} = 101_2$$

$$7_{10} = 111_2$$

$$17_{10} = 10001_2$$

$$143_{10} = 10001111_2$$

$$34_{10} = 100010_2$$

$$53_{10} = 110101_2$$

We know how to add two decimal numbers but let us review the process since we can use it as a guide to binary addition.

Add without carries:

$$\begin{array}{r} 34 \\ + 5 \\ \hline 39 \end{array}$$

Here we can add the  $5 + 4$  and get a number smaller than 10; therefore, there is no carry into the 10's column.

$$\begin{array}{r} 27 \\ + 61 \\ \hline 88 \end{array}$$

Again the sum in each column is less than 10; there are no carries so each column can be added independently.

Add with carries:

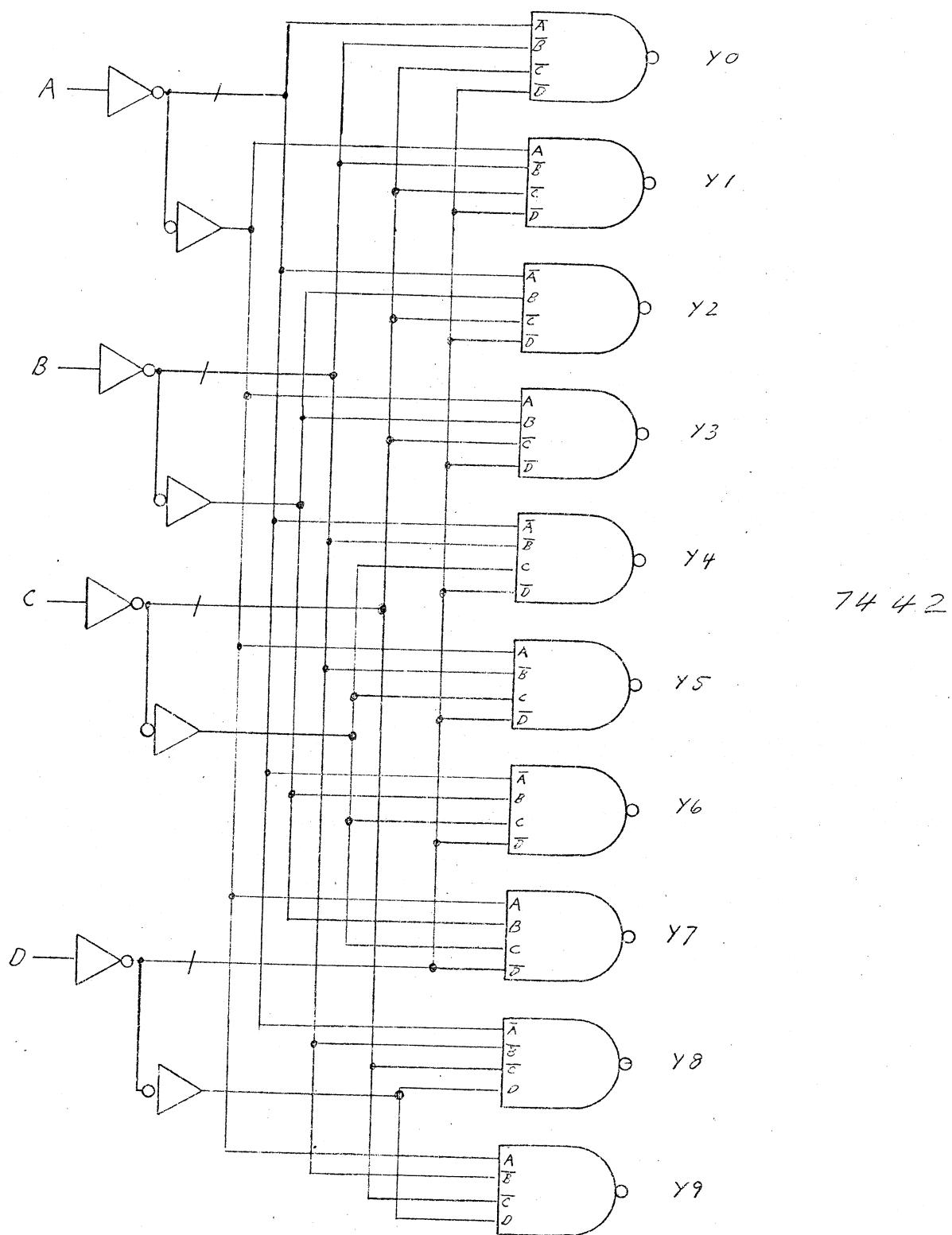

$$\begin{array}{r} 7 \\ + 5 \\ \hline 12 \end{array}$$

Here the situation is slightly more complex. The largest digit we can have in any column is 9, but  $7 + 5$  is larger than 9. We solve this by a carry into the 10's column which says  $7 + 5 = 10 + 2$ . Remember the carry = 10 and the 2 is how much we have to add to the 10 to get the answer.

It is somewhat unconventional but we can show this very nicely in the following fashion:

Consider more complex examples:

$$\begin{array}{r}

6 \ 9 \\

+ 5 \ 2 \\

\hline

1 \ 2 \ 1

\end{array}

\text{SUM}$$

$$\begin{array}{r}

5 \ 6 \ 7 \\

+ 2 \ 4 \ 1 \\

\hline

8 \ 0 \ 8

\end{array}

\text{SUM}$$

$$\begin{array}{r}

4 \ 5 \ 6 \ 7 \\

+ 5 \ 4 \ 3 \ 3 \\

\hline

1 \ 0 \ 0 \ 0 \ 0

\end{array}

\text{SUM}$$

The rules describing this process are:

- The number of different digits is 10 (0, 1, . . . 9).

- If the sum in a given column is less than 10 there is no carry into the next column.

- If the sum in a given column is 10 or more there is a carry into the next column.

Analogous rules hold for binary addition:

- The number of different digits is 2 (0, 1)

- If the sum in a given column is less than 2 there is no carry.

- If the sum in a given column is 2 or more there is a carry.

To show how similar decimal and binary addition are we will do the same example side by side.

$$7_{10} = 111_2$$

$$5_{10} = 101_2$$

$$\begin{array}{r}

7 \\

+ 5 \\

\hline

1 \ 2

\end{array}

\text{SUM}$$

$$\begin{array}{r}

1 \ 1 \ 1 \\

+ 1 \ 0 \ 1 \\

\hline

1 \ 1 \ 0

\end{array}

\text{SUM}$$

$$1100_2 = 12_{10}$$

$$2_{10} = 10_2$$

$$\begin{array}{r}

2 \\

+ 2 \\

\hline

4

\end{array} \text{ SUM}$$

$$2_{10} + 2_{10} = 4_{10}$$

$$\begin{array}{r}

1 0 \\

+ 1 0 \\

\hline

1 0

\end{array} \text{ SUM}$$

$$100_2 = 4_{10}$$

$$17_{10} = 10001_2$$

$$\begin{array}{r}

1 7 \\

+ 9 \\

\hline

2 6

\end{array} \text{ SUM}$$

$$9_{10} = 1001_2$$

$$\begin{array}{r}

1 0 0 0 1 \\

+ 1 0 0 1 \\

\hline

1 1 0 0 0

\end{array} \text{ SUM}$$

$$11010_2 = 26_{10}$$

In the preceding examples we assumed you knew the addition tables. For binary addition the tables are very simple:

| carry from preceding column | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

|-----------------------------|---|---|---|---|---|---|---|---|

| A                           | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| + B                         | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 |

| SUM                         | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 |

| carry to next column        | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 |

This same information is more usually arranged in a form that looks like a truth table.  $C_i$  represents a carry into this column.  $C_o$  represents a carry out of this column.

| $C_i$ | A | B | S | $C_o$ |

|-------|---|---|---|-------|

| 0     | 0 | 0 | 0 | 0     |

| 0     | 0 | 1 | 1 | 0     |

| 0     | 1 | 0 | 1 | 0     |

| 0     | 1 | 1 | 0 | 1     |

| 1     | 0 | 0 | 1 | 0     |

| 1     | 0 | 1 | 0 | 1     |

| 1     | 1 | 0 | 0 | 1     |

| 1     | 1 | 1 | 1 | 1     |

IMPORTANT PROBLEM!

$$\text{Prove: } S = A \oplus B \oplus C_i$$

$$\begin{aligned}

C_o &= A \cdot B + A \cdot C_i + B \cdot C_i \\

&= A \cdot B + C_i (A + B)

\end{aligned}$$

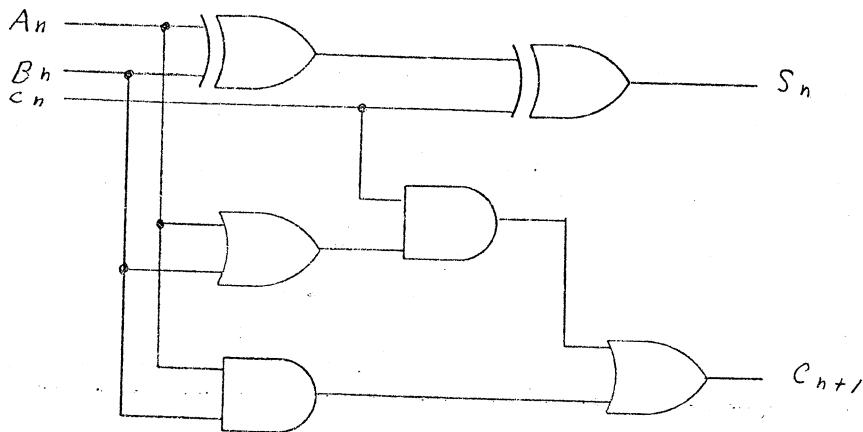

These equations can be translated to hardware as shown below:

We have changed the nomenclature slightly.  $A$ ,  $B$  have been subscripted with a small  $n$  to signify that we are working with column  $n$  of a binary number.  $C_n$  denotes the carry into column  $n$  and  $C_{n+1}$  denotes the carry out of this column.

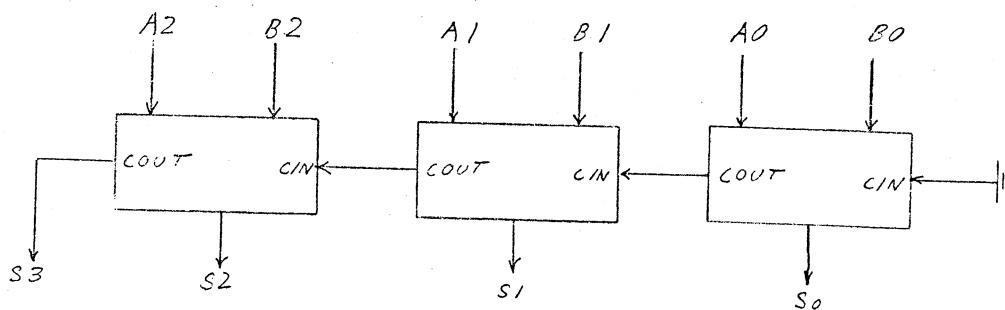

Let us enclose the above circuit in a special symbol box and show how adders can be connected together to add two 3 bit numbers. Label the columns as follows:

$$\begin{array}{r}

A_2 \quad A_1 \quad A_0 \\

+ B_2 \quad B_1 \quad B_0 \\

\hline

S_3 \quad S_2 \quad S_1 \quad S_0

\end{array}$$

Note that  $C_0 = 0$ ; therefore it is tied to ground to make it always L.

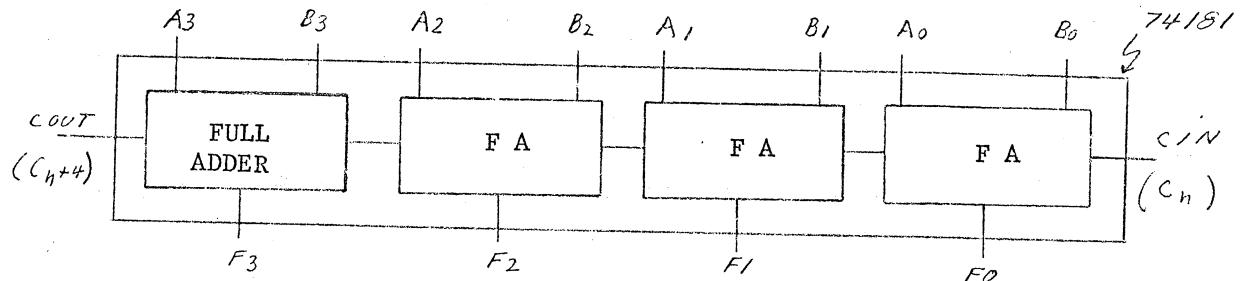

One might think that the full adder would be available as an IC. Indeed it is; but a more common IC (7483) contains 4 full adders in a single package. The carry lines are internally connected so there are only two carry lines; C in to the 4 bit group and C out of the 4 bit group.

## SUBTRACTION

We could go through an analogous procedure to derive the algorithm for subtraction and finally wind up with hardware to do it. Fortunately we can use an adder to subtract. We will base our discussion on an ordinary electronic calculator with 6 digits of accuracy. If one is not available you can think of an imaginary 3 digit calculator. Our immediate goal is to use such a calculator to subtract by using only the add key.

To do this we need to define a complement number. In the following discussion we will assume our imaginary 3 digit calculator. If you have an electronic hand calculator by all means use it to do the same examples.

To form a 3 digit complement of a number  $n$ , subtract it from 1000.

$$\begin{array}{r} \text{Complement of } 237 = 1000 - 237 = 763 \\ \text{Complement of } 64 = 1000 - 64 = 936 \\ \text{Complement of } 700 = 1000 - 700 = 300 \end{array}$$

Let us subtract first using normal arithmetic and secondly by addition of a complement.

$$\begin{array}{r} 514 \\ - 237 \\ \hline 277 \end{array} \quad \begin{array}{r} 514 \\ + 763 \\ \hline 1277 \end{array} \quad \begin{array}{r} 514 \\ - 64 \\ \hline 450 \end{array} \quad \begin{array}{r} 514 \\ + 936 \\ \hline 1450 \end{array}$$

In each case the answer obtained by complement addition is exactly 1000 larger than the number obtained by normal subtraction. This of course must be true since a complement is formed by subtraction from 1000.

$$514 + (1000 - 237) = 1000 + (514 - 237)$$

We see that we could do a subtraction very nicely by complement addition if: a) we had an easy way to reject the 1000,

b) we had an easy way to independently form the complement.

Fortunately the first is automatic. We assumed we had only a 3 digit calculator. The 1000 lies in the fourth column so it is automatically discarded.

The second problem is only slightly more complicated. We need some way of subtracting the number from 1000 that is so easy that it does not burden the process. The main problem in subtraction for humans is the borrow problem. If only we could devise a way to subtract column by column without a borrow we could write the complement almost as fast as we could write the original number. There is an easy way to do this:

$$1000 = 999 + 1$$

$$1000 - 237 = (999 - 237) + 1$$

Now it is impossible to get a borrow in subtracting any three digit number from 999. You can see this by considering only one column at a time.

The largest digit you can have is a 9 and a  $9-9 = 0$  with no borrow. Since we have no borrows we can now subtract from right to left or left to right. Let's use this procedure to form the complement of some numbers.

Complement of 237:

$$\begin{array}{r} 9 & 9 & 9 \\ - 2 & - 3 & - 7 \\ \hline 7 & 6 & 2 \end{array} + 1$$

So to subtract 237 from 514

add

$$\begin{array}{r} 514 \\ + 762 \\ \hline 1276 \end{array}$$

then add 1

$$\begin{array}{r} 1276 \\ + 1 \\ \hline 1277 \end{array}$$

└ automatically discarded

NOTE: We have used only the addition process. (We assumed an independent easy way for forming complements).

Complement of 64:

$$\begin{array}{r} 9 & 9 & 9 \\ - 0 & - 6 & - 4 \\ \hline 9 & 3 & 5 \end{array} + 1$$

$$\begin{array}{r} 514 & 514 & \text{add 1} & 1449 \\ - 64 & + 935 & + 1 & \hline 450 & 1449 & 1450 \end{array}$$

└ automatically discarded

We call the number obtained by subtracting from 999 the NINE's complement. We define the number obtained by subtracting from 1000 the TEN's complement. Thus:      TENS Complement = NINES Complement + 1

Again the reason for breaking the tens complement up into two steps is the ease of doing each step.

Now let us see how we can handle a calculator of more than three digits. The crucial thing is the automatic discard of the one to the left of the difference:

For a 3 digit calculator use  $1000 = 10^3$

For a 4 digit calculator use  $10000 = 10^4$

For a 6 digit calculator use  $1,000,000 = 10^6$

For an  $n$  digit calculator use  $1,000 \dots = 10^n$

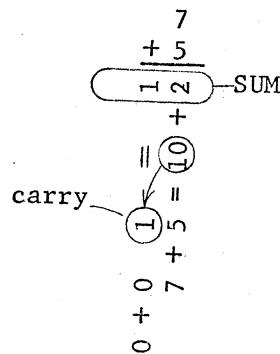

Now that we have shown how complement addition works for decimal numbers, we can move to binary numbers. The process of taking complements is even easier in binary. By analogy with the calculator example if our binary computer has  $n$  bits the complement will be formed by subtracting from  $2^n$ . Definition: 2's complement of  $x = 2^n - x$ .

For example suppose we have a 3 bit machine:

$$\begin{array}{r} 7 \\ - \frac{5}{2} \\ \hline 11 \end{array} \quad \text{2's complement of } 5 = 1000$$

$$\begin{array}{r} 111 \\ + 11 \\ \hline 1010 \end{array}$$

$$010_2 = 2_{10}$$

automatically discarded since have only a 3 bit machine.

We will find that it much easier to take the complement in two steps as we did for decimal numbers.

$$\begin{array}{r} 2^3 = 1000_2 = 111 + 1 \\ \begin{array}{r} 111 \\ - 101 \\ \hline 010 \end{array} \end{array}$$

NOTE: The final result is a bit by bit NOT (complement) of the denominator.

Definition: The ONE's complement of a binary number is formed by changing each 1 to a 0 and each 0 to a 1.

TWO's complement of  $X$  = ONE's complement of  $X + 1$ .

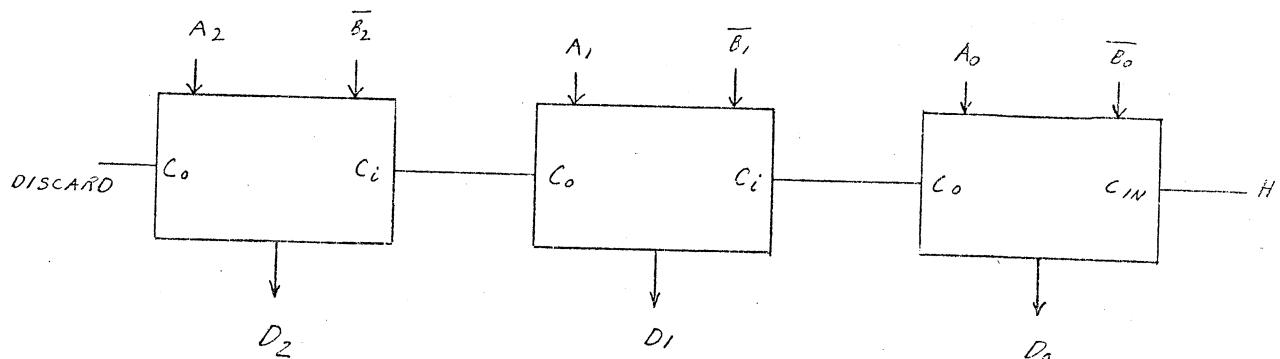

As you can guess the ones complement of a binary number is very easy to generate electronically. Further the extra 1 to be added can be generated simply by turning on the carry in to the right most adder (for addition it is always turned off).

We can show this process by means of a logic diagram.

We have studied most of the combinatorial elements required for a computer. The last and most important one will be covered in this chapter. It is called the arithmetic logic unit (ALU). Its function is to take data words and perform arithmetic operations (such as add) or logical operations (such as AND) in response to instructions from a program stored in memory.

Building an arithmetic unit with early integrated circuits was quite a chore since only simple gates and inverters were available. Such IC's are called SSI (Small Scale Integrated) circuits. Technology has progressed to the point where more complex circuits can now be manufactured. MSI (Medium Scale Integration) contains circuits of approximately 100 gates per IC. LSI (Large Scale Integration) contains approximately 1000 gates per package. The computer you will construct uses all three classes of IC's. SSI is used for implementing simple logic equations. LSI is used in the memory and MSI is used to build the arithmetic unit.

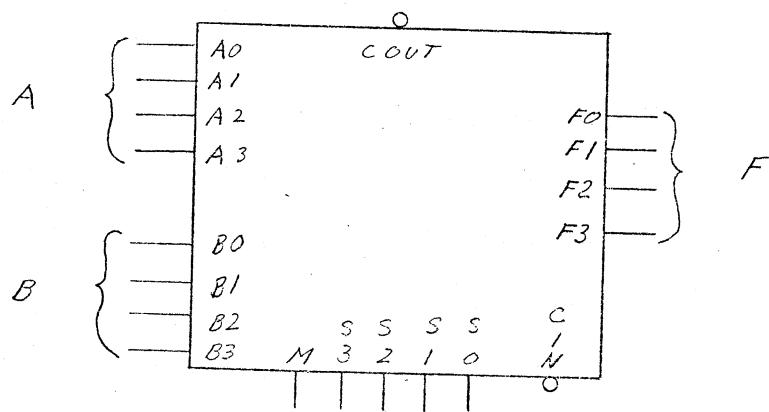

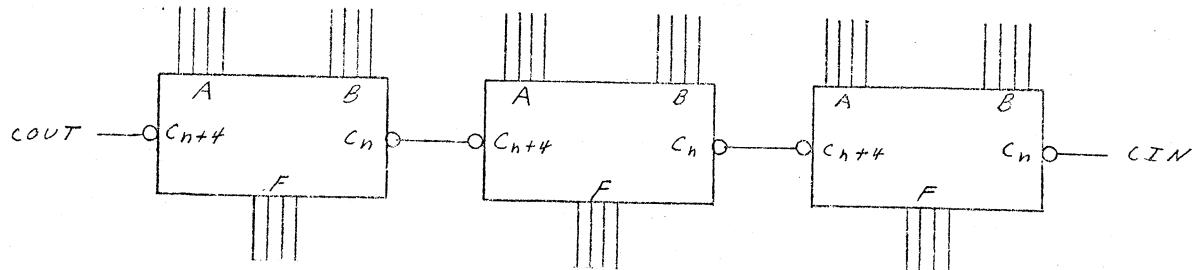

The MSI circuit you will use is a remarkable device. It will be worth studying it in detail since it is the heart of the computer. The device is the 74181 which is capable of performing all possible logical operations (AND, OR, etc.) as well as arithmetic operations on two 4 bit operands. These devices can be strung together to form arithmetic units which will handle more than 4 bits. Since our computer is a 12 bit machine, it will require three 74181's. The symbol for the device is:

A, B, and  $C_{in}$  are the inputs; F and  $C_{out}$  are the outputs. M and S are control inputs which tell the ALU what operation to perform on A, B, and  $C_{in}$ .

Since there are five control inputs  $32 (2^5)$  different operations can be performed by the 74181. These are broken down into two groups of 16 based on the value of M. When M = L it will do arithmetic operations (adding) and when M = H it will do logic operations. You may wonder how these can be 16 such operations since we have discussed only NOT, AND, OR, and EXCLUSIVE OR. Let us imagine a "black box" with two inputs A, B, and one output F. The question we are asking is how many different kinds of "black boxes" can there be. This in turn forces us to ask how

do we know when we have a particular "black box," such as an AND gate. The answer is of course by means of the truth table that the black box produces. For example if we input all four combinations of A, B and obtain this output on F:

| A | B | F |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Then we know that this particular black box is indeed an AND gate. There are exactly 16 different possible truth table outputs as shown below: